# **Data Sheet**

SPATIALIZER<sup>®</sup> 3-D STEREO

## DESCRIPTION

The ES938 is an audio effects processor, generating 3-D audio with bass and treble tone controls. It uses a built-in *Spatializer*<sup>®</sup> 3-D Stereo Processor to convert existing stereo and mono audio input signals into immersive 3-D audio using only two conventional speakers. Instead of a limited field of sound emitted by the left and right speakers alone, spatialized sound is transmitted in a wider arc (up to 270° around the listener), creating the atmosphere of a resonant 3-D sound environment.

The enhanced sound imaging of the ES938 can be incorporated into any audio circuit to automatically provide a 3-D sound that expands beyond the speakers. The builtin serial interface also provides separate *Spatializer*, bass, and treble controls for audio programming. These controls can each be independently switched in or out for maximum user control over individual features.

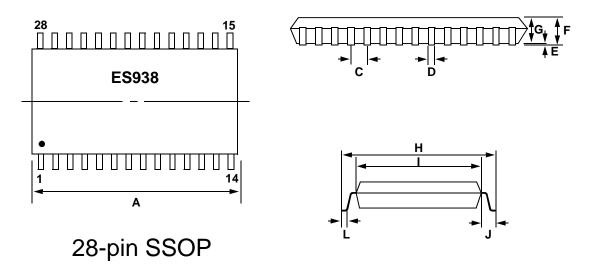

The ES938 is available in an industry-standard 28-pin Super Small Outline Package (SSOP).

# FEATURE HIGHLIGHTS

- Single low-cost IC provides *Spatializer* 3-D stereo sound effects

- Immersive 3-D audio from any audio input

- Bass and treble controls

- MIDI Serial interface for digital control of native features

- Expands the sound stage of stereo and mono audio material for a fuller sound environment from only two speakers

- · On/off pins enable and disable features

## APPLICATIONS

- Audio/Video Systems

- Consumer Audio Products

- Game Machines

- Motherboards

- Multifunction Add-in Cards

- Multimedia PCs

- Notebook PCs

- PC Sound Cards

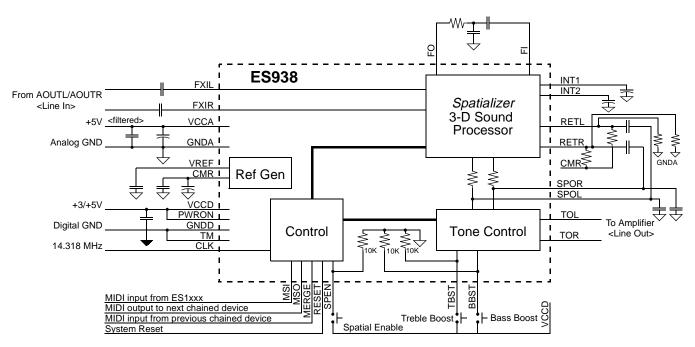

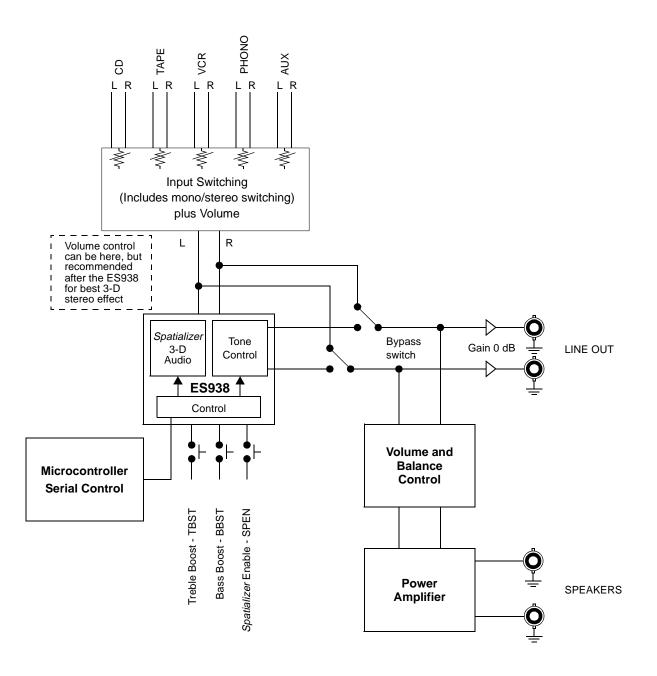

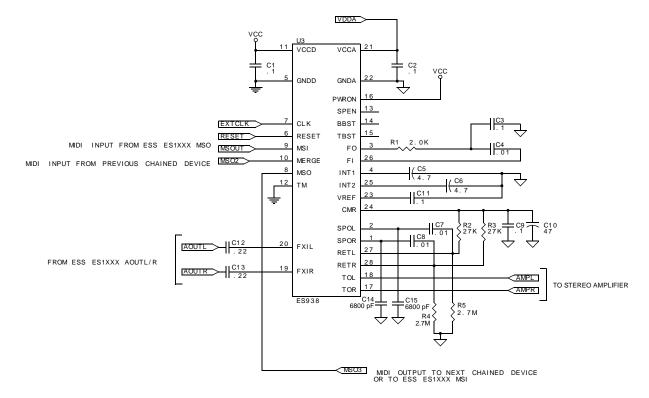

Figure 1 ES938 Typical Application

CONTENTS

# CONTENTS

| DESCRIPTION 1                                   |

|-------------------------------------------------|

| FEATURE HIGHLIGHTS 1                            |

| APPLICATIONS 1                                  |

| PINOUT                                          |

| PIN DESCRIPTIONS 4                              |

| Digital Pin Descriptions 4                      |

| Analog Pin Descriptions                         |

| FUNCTIONAL DESCRIPTION                          |

| MIDI Register Control Interface                 |

| Register Write System Exclusive Messages 5      |

| Register Read System Exclusive Messages and the |

| MERGE Pin                                       |

| REGISTERS                                       |

|                                                 |

# FIGURES

| Figure 1 ES938 Typical Application1                  |

|------------------------------------------------------|

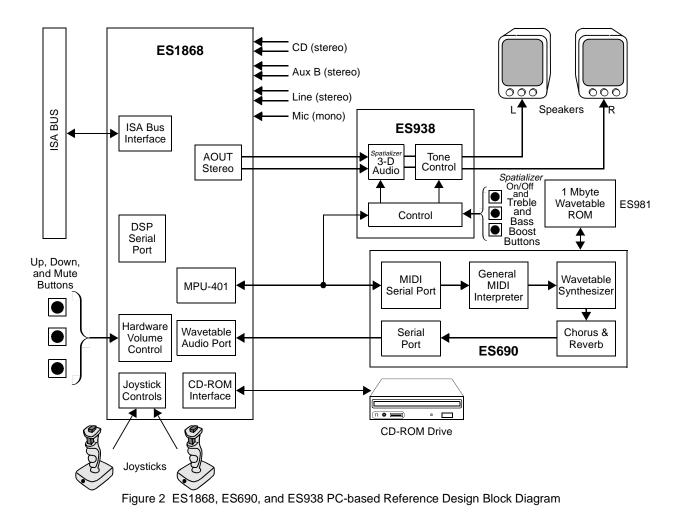

| Figure 2 ES1868, ES690, and ES938 PC-based Reference |

| Design Block Diagram 2                               |

| Figure 3 The ES938 Pinout 4                          |

| Figure 4 Output Bypass During Power Down and Reset 7 |

| Figure 5 | Typical Spatializer Implementation |

|----------|------------------------------------|

| Figure 6 | Clock Timing Diagrams              |

| Figure 7 | Mechanical Dimensions              |

| Figure 8 | ES938 Schematic                    |

## PINOUT

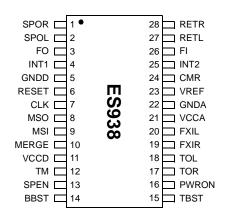

Figure 3 The ES938 Pinout

## **PIN DESCRIPTIONS**

#### **Digital Pin Descriptions**

| Pin   | I/O | Description                                                                                                                                                                                                                                                          |

|-------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCCD  | Ι   | Digital power supply, 3.0 - 5.5 V.                                                                                                                                                                                                                                   |

| GNDD  | Ι   | Digital ground.                                                                                                                                                                                                                                                      |

| CLK   | Ι   | 14.318 MHz clock input.                                                                                                                                                                                                                                              |

| RESET | Ι   | Active-high reset input from ISA bus.                                                                                                                                                                                                                                |

| ТМ    | Ι   | Test pin; connect to digital ground.                                                                                                                                                                                                                                 |

| MSO   | 0   | MIDI serial output; connect to MIDI serial<br>input of audio controller.                                                                                                                                                                                             |

| MSI   | I   | MIDI serial input; connect to MIDI serial out-<br>put of audio controller.                                                                                                                                                                                           |

| MERGE | I   | MIDI serial input from external MIDI devices.<br>Except when the ES938 is transmitting, this<br>pin is internally connected to the MSO pin.                                                                                                                          |

| SPEN  | I   | Input with internal pull-down device. When<br>high (digital or analog VCC), enables spa-<br>tialization effect at current limit level (limit<br>level is set to maximum by reset). The inter-<br>nal pull-down device is disabled when the<br>ES938 is powered down. |

| TBST  | I   | Input with internal pull-down device. When<br>high (digital or analog VCC), enables treble<br>boost, overriding current internal tone con-<br>trol setting. The internal pull-down device is<br>disabled when the ES938 is powered down.                             |

| BBST  | I   | Input with internal pull-down device. When<br>high (digital or analog VCC), enables bass<br>boost, overriding current internal tone con-<br>trol setting. The internal pull-down device is<br>disabled when the ES938 is powered down.                               |

| PWRON | Ι   | Input with internal pull-down device. When low, the ES938 is powered down.                                                                                                                                                                                           |

## **Analog Pin Descriptions**

| Pin  | I/O | Description                                                                                                                                                  |

|------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCCA | Ι   | Analog power supply, 5 V $\pm$ 10%. Should be greater than or equal to VDDD-0.3 V.                                                                           |

| GNDA | Ι   | Analog ground.                                                                                                                                               |

| VREF | 0   | 2.25 V reference resistor divider output. Should be bypassed to analog ground with 0.1 $\mu F$ capacitor.                                                    |

| CMR  | 0   | Buffered common mode reference output. Should be bypassed to analog ground with a 47 $\mu$ F electrolytic capacitor with a .1 $\mu$ f capacitor in parallel. |

| FXIL | Ι   | Signal input, left channel.                                                                                                                                  |

| FXIR | Ι   | Signal input, right channel.                                                                                                                                 |

| SPOL | 0   | Left channel Spatializer output.                                                                                                                             |

| SPOR | 0   | Right channel Spatializer output.                                                                                                                            |

| RETL | Ι   | Left channel tone control input.                                                                                                                             |

| RETR | Ι   | Right channel tone control input.                                                                                                                            |

| INT1 | Ι   | Connect to external 4.7 $\mu$ F capacitor (which connects to analog ground).                                                                                 |

| INT2 | Ι   | Connect to external 4.7 $\mu$ F capacitor (which connects to analog ground).                                                                                 |

| FO   | 0   | Output connected to FI via external capacitor/ resistor network.                                                                                             |

| FI   | I   | Input connected to FO via external capacitor/<br>resistor network.                                                                                           |

| TOL  | 0   | Left channel output of tone control.                                                                                                                         |

| TOR  | 0   | Right channel output of tone control.                                                                                                                        |

FUNCTIONAL DESCRIPTION

## FUNCTIONAL DESCRIPTION

### **MIDI Register Control Interface**

The ES938 is controlled from the host processor by using the System Exclusive (Sysex) command through a MIDI serial link. The command format is:

F0 <id> <command> <address> <data> [<address> <data> ...] F7

#### where:

| F0                  | MIDI System Exclusive start.                                           |

|---------------------|------------------------------------------------------------------------|

| <id></id>           | Three-byte manufacturer code for ESS<br>Technology. The ID is 00 00 7B |

| <command/>          | Command for register read is 7E. Command for register write is 7F.     |

| <address></address> | ES938 register address, 00–07H.                                        |

| <data></data>       | Data to be written into register for write                             |

command. Not used for read command.

F7 MIDI System Exclusive end.

The register read command responds with a System Exclusive message as follows:

F0 <id> 7E <address> F7

### **Register Write System Exclusive Messages**

If the host software is not currently doing MIDI I/O, it can simply enable the MPU-401 port and transmit the System Exclusive command to write one or more of the ES938 registers.

If the host software is actively transmitting MIDI data, then the System Exclusive message must be inserted into the data stream in such a way as to not cause a conflict. This means that the host software must keep track of the data being transmitted, so that it can know when it can transmit the System Exclusive message.

- 1. Do not transmit in the middle of a multi-byte MIDI message. Only transmit between MIDI messages. For example, a note-on message has three bytes (two bytes if it is a Running Status message); do not transmit in the middle of this message. Also, do not transmit in the middle of a System Exclusive message.

- 2. Keep track of the current Running Status state. After the System Exclusive is transmitted, the Running Status state is probably corrupted by devices receiving the System Exclusive. Therefore, if the next data to be transmitted does not start with a new status byte, insert a status byte. A status byte is defined as a MIDI byte between 80h and F7h.

- 3. At the time the System Exclusive is transmitted, the Running Status state may be unknown. Or you don't want to send the System Exclusive for reasons listed

above, but a time-out elapses. In either case, after the System Exclusive, discard transmitted bytes up until the next status byte.

### **Register Read System Exclusive Messages and** the MERGE Pin

Normally, the MERGE input is connected to MSO (MIDI Serial Output pin) inside the ES938. When the ES938 is transmitting in reply to a register read command, it must disconnect MERGE and drive MSO.

The ES938 has logic that prevents the switch away from MERGE until 10 bit periods have passed while the MERGE pin remains high. The purpose is to prevent switching while serial data is being transmitted. For this reason, the host software must read and process (or discard) incoming data until the System Exclusive and manufacturer ID bytes are received.

Of course, it is possible that incoming MIDI data to the MERGE pin will be lost while the System Exclusive message is being transmitted. If the host software was in the middle of reading a multi-byte MIDI message, that message must be assumed to be corrupted, and therefore it should be discarded.

At the end of the System Exclusive transmission, the ES938 will switch the MSO pin back to the MERGE pin. However, before it does so, it must see 10 bit periods pass while the MERGE pin remains high.

After the host software receives the System Exclusive message, it should discard Running Status messages until a new status byte is received.

# REGISTERS

| Register 0 Miscellaneous Control Register |                                                      |                                                                      |         |         |            | egister | Regist       | ers 2, 3 | 3, 4            |               |          | Res              | erved (V    | Vrite 0)     |

|-------------------------------------------|------------------------------------------------------|----------------------------------------------------------------------|---------|---------|------------|---------|--------------|----------|-----------------|---------------|----------|------------------|-------------|--------------|

| 7                                         | 6                                                    | 5 4                                                                  | 3       | 2       | 1          | 0       | 7            | 6        | 5               | 4             | 3        | 2                | 1           | 0            |

| 0                                         | 1                                                    | TIL                                                                  | I       | NG      | DE         | 3       | 0            | 0        | 0               | 0             | 0        | 0                | 0           | 0            |

| Reset:                                    | 49h                                                  |                                                                      | ·       |         |            |         |              |          |                 |               |          |                  |             |              |

| Bit 6                                     | 1                                                    |                                                                      |         |         |            |         | Regist       | er 5     |                 | S             | patializ | z <i>er</i> Effe | ect Limi    | t/Mode       |

| Bit 5:4                                   | TIL                                                  |                                                                      |         |         |            |         | 7            | 6        | 5               | 4             | 3        | 2                | 1           | 0            |

|                                           |                                                      | Block Input input of the                                             |         |         |            | nuator  | 0<br>Bit 7:0 | SPC5     | SPC4            | SPC3          | SPC2     | SPC1             | SPC0        | R<br>R       |

|                                           | 00<br>01<br>10                                       | 0 dB<br>-3 dB<br>-6 dB                                               |         |         |            |         |              | Reg      |                 | ttings n      |          |                  | nt of 3-D   | ) effect.    |

|                                           | 11                                                   | -9 dB                                                                |         |         |            |         |              |          |                 |               |          |                  |             |              |

| Bit 3:2                                   | NG                                                   |                                                                      |         |         |            |         |              | 47h      | : minim         | um effe       | ct level |                  |             |              |

|                                           |                                                      | e Gate.                                                              |         |         |            |         |              | 5Bh      | : mediu         | m effec       | t level  |                  |             |              |

|                                           |                                                      | setting on th<br>=0, NG1=1                                           | ese two | bits mu | ist be:    |         |              | 67h      | : maxim         | num effe      | ect leve | el               |             |              |

| Bit 1:0                                   | DB                                                   |                                                                      |         |         |            |         | Regist       | er 6     |                 |               |          |                  |             |              |

|                                           |                                                      | e values m<br>=0, DB0=1).                                            |         | set to  | a value    | e of 1  | 7            | 6        | <b>Ѕра</b><br>5 | tializer<br>4 | Proces   | ssor E           | nable R     | egister<br>0 |

|                                           | (==:                                                 | 0, 220 .)                                                            |         |         |            |         | 0            | 0        | 0               | 0             | 0        |                  | Spatializer |              |

| Registe                                   | r 1                                                  |                                                                      | Т       | one Co  | ntrol Re   | egister |              |          |                 |               |          |                  |             |              |

| 7                                         | 6                                                    | 5 4                                                                  | 3       | 2       | 1          | 0       | Reset:       | 00F      | 1               |               |          |                  |             |              |

| 0                                         | Iret                                                 | ole Control                                                          | 0       | В       | ass Contro | ol      | Bit 1:0      | Spa      | atialize        | Proces        | ssor E   | nable F          | Register    |              |

| Reset:                                    | 33h                                                  |                                                                      |         |         |            |         | 02h          | Disa     | able Sp         | atializer     | r Proce  | ssor             |             |              |

| Bit 6:4                                   | Trebl                                                | e Control                                                            |         |         |            |         | 03h          | Ena      | ble Spa         | atializer     | Proces   | ssor             |             |              |

|                                           | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | -9 dB<br>-6 dB<br>-3 dB<br>0 dB<br>+3 dB<br>+6 dB<br>+9 dB<br>+12 dB |         |         |            |         |              |          |                 |               |          |                  |             |              |

| Bit 2:0                                   | Bass                                                 | Control                                                              |         |         |            |         |              |          |                 |               |          |                  |             |              |

|                                           | 000<br>001<br>010<br>011                             | -9 dB<br>-6 dB<br>-3 dB<br>0 dB                                      |         |         |            |         |              |          |                 |               |          |                  |             |              |

+3 dB

+6 dB

+9 dB

+12 dB

100

101

110

111

#### REGISTERS

| Register 7 Power Control Registe |   |   |   |   |                             |                  |               |  |

|----------------------------------|---|---|---|---|-----------------------------|------------------|---------------|--|

| 7                                | 6 | 5 | 4 | 3 | 2                           | 1                | 0             |  |

| R                                | R | R | R | R | Enable<br>Pullups<br>FXIL/R | Output<br>Enable | Power<br>Down |  |

Reset: 0Eh

Bit 7:3 Reserved

- Bit 2 Enable Pullups FXIL, FXIR

- 0: No pullups to 2.25 V on pins FXIL, FXIR when powered down.

- 1: Pullups enabled when powered down (except when input PWRON=0, in which case the pullups are always defeated).

#### Bit 1: Output Enable

- 0: Output Bypass

- 1: Output Enable

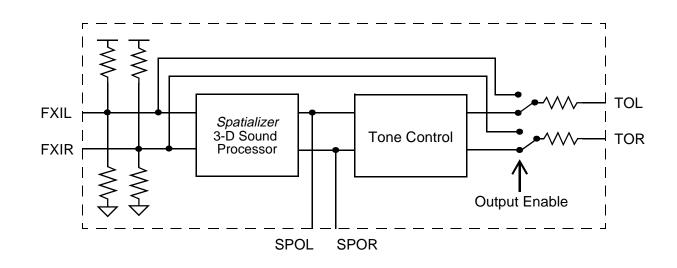

When bit 1 is 0, the entire ES938 analog section is bypassed. Outputs TOL and TOR are internally connected to inputs FXIL and FXIR. Inputs FXIL and FXIR have highvalue pullups to approximately the voltage of the CMR. Bypass is also enabled when powered down when the reset input is high.

#### Bit 0 Power Down

- 0: Power Up

- 1: Power Down

Figure 4 Output Bypass During Power Down and Reset

# TYPICAL CONSUMER AUDIO ELECTRONICS APPLICATION

Figure 5 Typical Spatializer Implementation

ELECTRICAL SPECIFICATIONS

# **ELECTRICAL SPECIFICATIONS**

## **Absolute Maximum Ratings**

| Rating                      | Symbol | Value         |

|-----------------------------|--------|---------------|

| Analog supply voltage       | VDDA   | -0.3 to 7.0 V |

| Digital supply voltage      | VDDD   | -0.3 to 7.0 V |

| Input voltage               | VIN    | -0.3 to 7.0 V |

| Operating temperature range | TA     | 0 to 70 °C    |

| Storage temperature range   | TSTG   | -50 to 125 °C |

## **DC Electrical Characteristics**

(over recommended operating conditions)

| Symbol | Parameter                 | Min  | Max       | Unit | Comments                        |

|--------|---------------------------|------|-----------|------|---------------------------------|

| VIH    | High-level input voltage  | 2.0  | VCC +0.25 | V    | All inputs TTL level except CLK |

| VIL    | Low-level input voltage   | -0.3 | 0.8       | V    | All inputs TTL level except CLK |

| VCH    | CLK high-level input      | 2.0  | VCC +0.25 | V    | TTL level input                 |

| VCL    | CLK low-level input       | -0.3 | 0.8       | V    | TTL level input                 |

| VOH    | High-level output voltage | 3.0  | -         | V    | IOH = 1mA                       |

| VOL    | Low-level output voltage  | -    | 0.45      | V    | IOL = 4mA                       |

| ILI    | Input leakage current     | -    | ±15       | μA   |                                 |

| ILO    | Output leakage current    | -    | ±15       | μA   |                                 |

| CIN    | Input capacitance         | -    | 10        | pF   | fc = 1 MHz                      |

| CO     | Input/output capacitance  | _    | 12        | pF   | fc = 1 MHz                      |

| CCLK   | CLK capacitance           | -    | 20        | pF   | fc = 1 MHz                      |

## **Extended DC Electrical Characteristics**

(over recommended operating conditions)

| Parameter                | Pins<br>(Conditions) | Min  | Тур  | Max   | Unit |

|--------------------------|----------------------|------|------|-------|------|

| Reference voltage        | VREF, CMR            | 2.00 | 2.25 | 2.50  | V    |

| Input impedance          | FXIL, FXIR           | 75k  | 100k | 125k  | Ω    |

| Output impedance         | SPOL, SPOR           | 750  | 1k   | 1.25k | Ω    |

|                          | TOL, TOR             | 5k   | 7.5k | 10k   | Ω    |

| Max voltage output swing | TOL, TOR             | -    | 2.5  | -     | Vpp  |

| IDDD operating current   | (CLK running)        | -    | 500  | 1k    | μA   |

|                          | (CLK stopped)        | -    | 10   | 50    | μA   |

| IDDA operating current   | (Power up)           | -    | 10   | 20    | mA   |

|                          | (Power down)         | -    | 10   | 50    | μA   |

## **AC Electrical Characteristics**

(over recommended operating conditions)

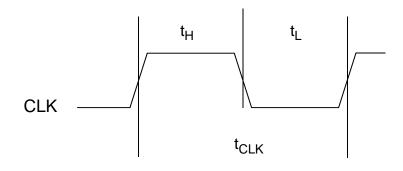

| Symbol           | Parameter              | Min | Тур             | Max | Unit |

|------------------|------------------------|-----|-----------------|-----|------|

| t <sub>CLK</sub> | Total clock cycle time | -   | 14.31818 ± 0.5% | -   | MHz  |

| t <sub>H</sub>   | Clock cycle high       | 40  | 70              | 100 | ns   |

| tL               | Clock cycle low        | 40  | 70              | 100 | ns   |

| t <sub>bit</sub> | MIDI bit period        | -   | 32.0 ± 0.5%     | -   | μs   |

## **Timing Diagrams**

Figure 6 Clock Timing Diagrams

10

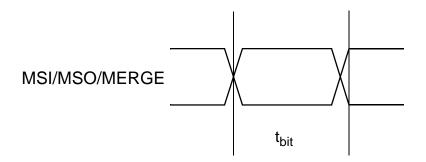

MECHANICAL DIMENSIONS

# **MECHANICAL DIMENSIONS**

| Symbol | Description               | Millimeters |       |       |  |

|--------|---------------------------|-------------|-------|-------|--|

|        |                           | Min         | Nom   | Max   |  |

| А      | Package's Outside, X-axis | 10.07       | 10.20 | 10.33 |  |

| С      | Lead pitch                | -           | 0.65  | -     |  |

| D      | Lead width                | 0.25        | -     | 0.38  |  |

| E      | Board standoff            | 0.05        | 0.13  | 0.21  |  |

| F      | Package height            | 1.73        | 1.86  | 1.99  |  |

| G      | Package thickness         | 1.68        | 1.73  | 1.78  |  |

| Н      | Foot print                | 7.65        | 7.80  | 7.90  |  |

| I      | Package's width, Y-axis   | 5.20        | 5.30  | 5.38  |  |

| J      | Lead length               | -           | 1.25  | -     |  |

| L      | Foot length               | 0.63        | 0.75  | 0.95  |  |

| -      | Coplanarity               | -           | -     | 0.076 |  |

| -      | Leads in x-axis           | -           | 14    | -     |  |

| -      | Total Leads               | -           | 28    | -     |  |

| -      | Package Type              | -           | SSOP  | -     |  |

Figure 7 Mechanical Dimensions

# **APPENDIX A: ES938 SCHEMATIC**

Figure 8 ES938 Schematic

# APPENDIX B: ES938 SCHEMATIC BILL OF MATERIALS (BOM)

| ltem | Quantity | Reference           | Part       |

|------|----------|---------------------|------------|

| 1    | 5        | C1, C2, C3, C9, C11 | 0.1 μF     |

| 2    | 2        | C12, C13            | 0.22 μF    |

| 3    | 3        | C4, C7, C8          | 0.01 μF    |

| 4    | 1        | C10                 | 47 μF      |

| 5    | 2        | C5, C6              | 4.7 μF     |

| 6    | 2        | C14, C15            | 6800 pF    |

| 7    | 1        | R1                  | 2k         |

| 8    | 2        | R2, R3              | 27k        |

| 9    | 2        | R4, R5              | 2.7M       |

| 10   | 1        | U3                  | ES938 SSOP |

ESS Technology, Inc. 48401 Fremont Blvd. Fremont, CA 94538 Tel: 510-492-1088 Fax: 510-492-1098 No part of this publication may be reproduced, stored in a retrieval system, transmitted, or translated in any form or by any means, electronic, mechanical, manual, optical, or otherwise, without the prior written permission of ESS Technology, Inc.

ESS Technology, Inc. makes no representations or warranties regarding the content of this document. All specifications are subject to change without prior

notice. ESS Technology, Inc. assumes no responsibility for any

ESS Technology, Inc. assumes no responsibility for any errors contained herein.

$(\mbox{P})$  U.S. Patent 4,214,125 and others, other patents pending.

Certain audio features of this product manufactured under a license from Desper Products, Inc., *Spatializer®* and the circle-in-square device are trademarks owned by Desper Products, Inc., U.S. patent numbers #4.308.423, #4.355.203, #5.412.731.

All other trademarks are owned by their respective holders and are used for identification purposes only.