# True-Color ChronDAC™ with 16-bit Interface

## **Features**

- · 16-bit pixel bus interface

- · On-chip clock doubler

- Three high speed 8-bit 110/135 MHz DACs

- Three high speed 256 x 6-bit color palette RAMs

- Compatible with ATT20C498 display modes

- · MIX-COLOR®: true on-the-fly mode switching

- 16.7M, 64K, 32K, and 256 color modes

- Supports 128/256 pseudo color, HICOLOR™2, 64K bypass, 16.7M bypass, XGA™ mode 2, and MIX-COLOR®

- Internal/external voltage reference or external current reference

- Drives singly or doubly terminated 75  $\Omega$  loads

- · ID register for software identification

- · Power down features for "Green PC" applications

- Anti-sparkle circuitry

- Dual-programmable 135 MHz PLL clocks

- · On-chip loop filters for PLL clocks

- Pin compatible to SGS-Thomson STG1703

- Low power CMOS technology in 68-pin PLCC

- 5V supply

## **Description**

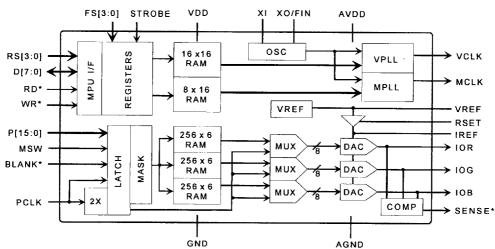

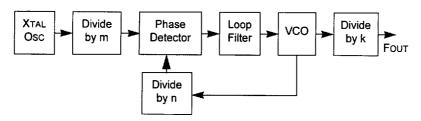

The CH8398 ChronDAC™ integrates two programmable PLLs, a triple 256 x 6-bit palette RAM, and a triple 8-bit 110/135 MHz video DAC. The video clock PLL provides 16 programmable frequencies, and the memory clock PLL provides 8 programmable frequencies.

The CH8398 pixel bus is 16 bits, twice the bandwidth of an 8-bit LUTDAC. The on-chip clock doubler allows CH8398 to support more colors with higher resolution while maintaining a lower pixel transfer rate.

Upon power up, the video clock is preset to 28.322 MHz and memory clock is preset to 40 MHz. After power up, video BIOS or driver software can initialize the PLL RAM entries to the desired values.

MIX-COLOR® mode provides the simultaneous display of maximum spatial resolution and color depth within a single bitmapped frame, efficiently utilizing memory. True on-the-fly mode switching occurs on a pixel-by-pixel basis, allowing 128/256 pseudo-color mode to be mixed with 64K color 5-6-5 or 32K color 5-5-5 bypass. Mixed mode switching can be controlled by hardware or software, easing design implementation.

CH8398 is fully compatible with VGA, VESA, Super-VGA, XGA<sup>TM</sup>, TARGA<sup>TM</sup>, 8514, and other non-standard frequencies, while providing many other enhanced features.

Figure 1: Block Diagram

# CHRONTEL

| Features and Description4 - 27Pinout Diagram CH83984 - 30Pin Description4 - 31Display Modes4 - 32Summary of Display Modes4 - 32 |

|---------------------------------------------------------------------------------------------------------------------------------|

| Pin Description       4 - 31         Display Modes       4 - 32         Summary of Display Modes       4 - 32                   |

| Display Modes       4 - 32         Summary of Display Modes       4 - 32                                                        |

| Display Modes       4 - 32         Summary of Display Modes       4 - 32                                                        |

| Summary of Display Modes                                                                                                        |

|                                                                                                                                 |

| Mode 0                                                                                                                          |

| Mode 1                                                                                                                          |

| Mode 2                                                                                                                          |

| Mode 3                                                                                                                          |

| Mode 4                                                                                                                          |

| Mode 5                                                                                                                          |

| Mode 6                                                                                                                          |

| Mode 7                                                                                                                          |

| Mode 8                                                                                                                          |

| Mode 9                                                                                                                          |

| Mode A                                                                                                                          |

| Mode B                                                                                                                          |

| Mode C                                                                                                                          |

| Mode D                                                                                                                          |

| Hardware and Software Mode Switching                                                                                            |

| Hardware Mode Switching         4 - 44           Software Mode Switching         4 - 44                                         |

| Bypass Mode Diagrams                                                                                                            |

| MIX-COLOR® 4 - 47                                                                                                               |

| MIX-COLOR®                                                                                                                      |

| Examples of Embedded Mode Switching for MIX-COLOR® and PixMix <sup>TM</sup>                                                     |

| PCLK Timing Diagrams                                                                                                            |

| Register Map4 - 54                                                                                                              |

| PWA: Palette RAM Write Address Register                                                                                         |

| PDR: Palette RAM Data Register                                                                                                  |

| RMR: Read Mask Register                                                                                                         |

| PRA: Palette RAM Read Address Register                                                                                          |

| CWA: PLL Clock RAM Write Address Register                                                                                       |

| CDR: PLL Clock RAM Data Register                                                                                                |

| CR: Control Register                                                                                                            |

| CRA: PLL Clock RAM Read Address Register 4 - 56                                                                                 |

| CSR: Clock Select Register                                                                                                      |

| IDR: Identification Register 4 - 57                                                                                             |

| TEST: Test Register                                                                                                             |

| AUX: Auxiliary Register                                                                                                         |

| MPU Access                                                | 4 - 58 |

|-----------------------------------------------------------|--------|

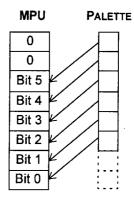

| Access to the Palette RAM                                 | 4 - 58 |

| 6-bit Access to the Palette RAM                           | 4 - 58 |

| Palette RAM Data Organization                             |        |

| Access to the PLL Clock RAM                               | 4 - 60 |

| PLL Clock RAM Data Organization                           | 4 - 60 |

| Alternate Access Method                                   | 4 - 61 |

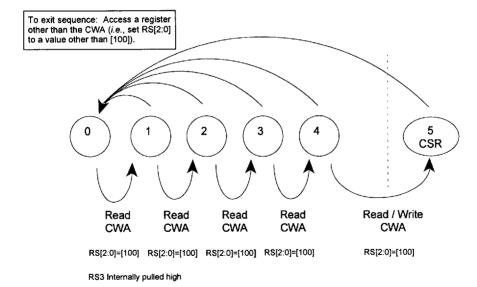

| Access to the Clock Select Register                       |        |

| Access to the Control Register                            |        |

| Access to the Identification Register                     |        |

| Access to the Auxiliary Register                          |        |

| PLL Clock Generator                                       |        |

| Sample Frequency Coefficients                             |        |

| Electrical Specifications                                 |        |

| Absolute Maximum Ratings                                  | 4 - 65 |

| Recommended Operating Conditions                          |        |

| DC Characteristics                                        | 4 - 65 |

| Digital Inputs / Outputs                                  | 4 - 66 |

| Clock Output Buffer                                       | 4 - 66 |

| Analog Outputs                                            | 4 - 66 |

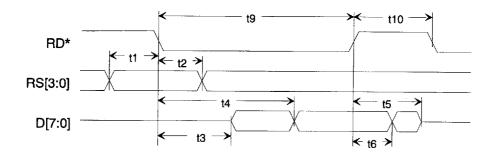

| AC Characteristics                                        | 4 - 67 |

| Timing Diagrams                                           | 4 - 68 |

| MPU Read Timing                                           | 4 - 68 |

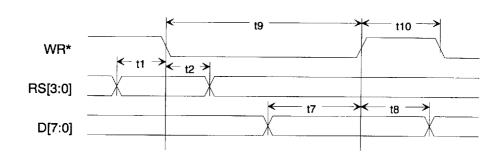

| MPU Write Timing                                          | 4 - 68 |

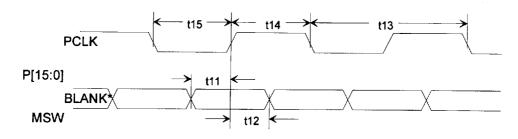

| Pixel Data, BLANK* Control Signal, and Mode Switch Timing | 4 - 68 |

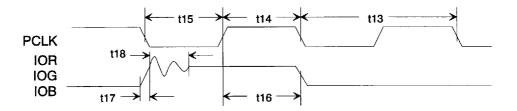

| DAC Output Timing                                         | 4 - 69 |

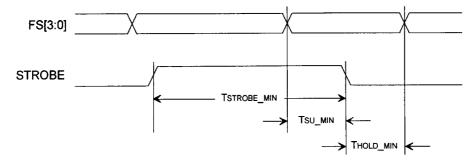

| Strobe Timing                                             | 4 - 69 |

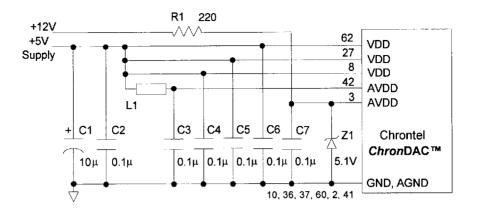

| PC Board Layout Considerations                            |        |

| Ground Planes                                             | 4 - 70 |

| Supply Decoupling                                         | 4 - 70 |

| Digital Signal Interconnect                               | 4 - 70 |

| Analog Signal Interconnect                                |        |

| Clock Signals                                             |        |

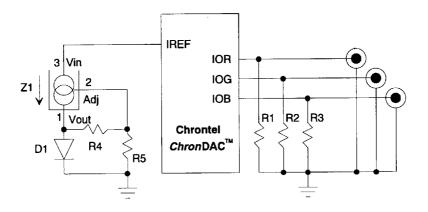

| Typical Connection Using External Current Reference       |        |

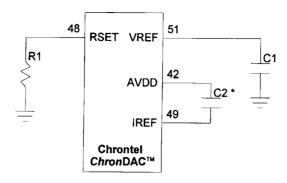

| Typical Connection Using Internal Voltage Reference       |        |

| Recommended Supply Decoupling                             |        |

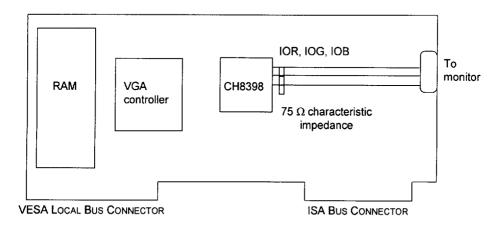

| Component Placement                                       |        |

| Ordering Information                                      | 4 - 74 |

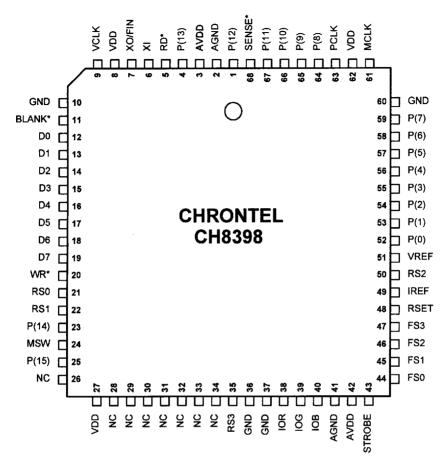

Figure 2: CH8398

Table 1 • Pin Description

| Pin#                                 | Symbol                                      | Type   | Name / Description                                                                                                                                                                                                                                                          |

|--------------------------------------|---------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 4, 23, 25,<br>52 – 59,<br>64 – 67 | P12, P13, P14,<br>P15, P0 – P7,<br>P8 – P11 | I      | Pixel. TTL compatible. Pixel data is latched on the rising edge of PCLK. Pseudo-color mode: pixel data is used as an address map to color palette RAM. Bypass color mode: pixel data represents actual color and directly drives DACs.                                      |

| 2, 41                                | AGND                                        | Р      | Analog Ground. AGND pins must be connected to system ground.                                                                                                                                                                                                                |

| 3, 42                                | AVDD                                        | Р      | Analog Power. AVDD pins must be connected to +5V.                                                                                                                                                                                                                           |

| 5                                    | RD*                                         | ı      | Read (Active Low). TTL compatible. RS[3:0] data is latched and transferred from selected register to data bus on falling edge of RD*.                                                                                                                                       |

| 6                                    | ΧI                                          | 1      | Crystal Oscillator. 14.318 MHz crystal or connect to GND if XO / FIN is connected to an external reference clock.                                                                                                                                                           |

| 7                                    | XO / FIN                                    | 1/0    | Crystal Oscillator / External Frequency. 14.318 MHz crystal or external reference clock input.                                                                                                                                                                              |

| 8, 27, 62                            | VDD                                         | P      | Digital Power. VDD pins must be connected to +5V.                                                                                                                                                                                                                           |

| 9                                    | VCLK                                        | 0      | Video Clock. TTL compatible. 28.322 MHz upon power up.                                                                                                                                                                                                                      |

| 10, 36, 37,<br>60                    | GND                                         | P      | Digital Ground. GND pins must be connected to system ground.                                                                                                                                                                                                                |

| 11                                   | BLANK*                                      | Ι      | <b>Blank (Active Low).</b> TTL compatible. BLANK* is latched on the rising edge of PCLK. When asserted, the analog outputs are turned off and the pixel inputs are ignored.                                                                                                 |

| 12 – 19                              | D0 –D 7                                     | 1/0    | Data Bus. TTL compatible. Bi-directional data bus.                                                                                                                                                                                                                          |

| 20                                   | WR*                                         | -      | Write (Active Low). TTL compatible. RS[3:0] data is latched on falling edge of WR*. D[7:0] data is latched on rising edge of WR*.                                                                                                                                           |

| 21, 22,<br>35, 50                    | RS0, RS1,<br>RS3, RS2                       | 1      | Register Select. TTL compatible. RS[3:0] data is latched on falling edge of RD* or WR*. RS[3:0] inputs determine which internal register to access. RS3 pin is internally pulled up to VDD.                                                                                 |

| 24                                   | MSW                                         | ł      | <b>Mode Switch.</b> TTL compatible with internal pull-down resistor. MSW is latched on the rising edge of PCLK. MSW input enables on-the-fly mode switching between primary and secondary modes.                                                                            |

| 26, 28 – 34                          | NC                                          | _      | No Connect. Unconnected pins.                                                                                                                                                                                                                                               |

| 38, 39, 40                           | IOR, IOG, IOB                               | 0      | Color Signals Output. Red, green, and blue DAC outputs, high impedance current sources capable of driving singly or doubly terminated 75 $\Omega$ load directly.                                                                                                            |

| 43                                   | STROBE                                      | I      | Strobe. TTL compatible with internal pull-up resistor. FS[3:0] inputs are latched on the falling edge of STROBE. The STROBE control pin should be held at VDD or left open for direct pass-through of FS[3:0]. For further details, please refer to Figure 22 on page 4-69. |

| 44 – 47                              | FS0 – FS3                                   | I      | External Video Clock Select. TTL compatible with internal pull-down resistor. FS[3:0] inputs are bit-wise "OR"ed with internal register CSR [3:0].                                                                                                                          |

| 48                                   | RSET                                        | Α      | Reference Resistor. This pin should be connected through an external 147 $\Omega\pm$ 1% resistor to GND. DAC output current levels are controlled by this resistor. See Note 2 below.                                                                                       |

| 49                                   | IREF                                        | Α      | Current Reference. External current reference input.                                                                                                                                                                                                                        |

| 51                                   | VREF                                        | A      | Voltage Reference. If using an external voltage source, supply this input with a 1.23V reference.                                                                                                                                                                           |

| 63                                   | PCLK                                        | 1      | Pixel Clock. TTL compatible. Pixel data is latched on the rising edge of PCLK.                                                                                                                                                                                              |

| 61                                   | MCLK                                        | 0      | Memory Clock. TTL compatible. 40 MHz upon power up.                                                                                                                                                                                                                         |

| 68                                   | SENSE*                                      | 0      | Sense (Active Low). TTL compatible. Monitor detect signal. SENSE* is logical 0 if one or more of the IOR, IOG, and IOB outputs has exceeded the internal voltage reference level of 340 mV.                                                                                 |

| Note 1:                              |                                             | Note 2 |                                                                                                                                                                                                                                                                             |

Note 1:

Note 2:

- I Input signal

- O Output signal

- I/O Bi-directional signal

- P Power pins

- A Analog signal

- $I_{FS} = \frac{V_{REF}}{R_{SET}} \times 2.1$

#### where

- · IFS is full-scale output current

- VREF is the voltage reference with value 1.23V

- RSET is the resistor connected between the RSET pin and ground, typical value is 147 W ± 1%

# **Display Modes**

Chrontel CH8398 offers two basic color modes: pseudo and bypass.

Pseudo-color mode: Pixel address (8-bit), after being lo

Pixel address (8-bit), after being logically "AND"ed with the pixel Read

Mask Register (RMR), is used to address all red, green, and blue palette

RAM.

Bypass color mode: Pixel data is used to drive inputs of the DACs directly, bypassing the palette

RAM and the RMR.

CH8398 provides 14 different display modes, each consisting of a primary and secondary mode. The pixel-by-pixel mode switching between primary and secondary modes is accomplished on-the-fly, and can be achieved through either hardware or software control.

Table 2 • Summary of Display Modes

| Mode | CR[7:4] | M              | SW = 0, PRIMARY MODE                   | Primary Mode Description                 | Colors |

|------|---------|----------------|----------------------------------------|------------------------------------------|--------|

| 0*   | 0000    | 8B1P1C         | 8 bpp, 1 pixel address, 1 PCLK cycle   | 8-bit pseudo                             | 256    |

| 1*   | 0001    | 15B1P1C        | 15 bpp, 1 pixel data, 1 PCLK cycle     | 15-bit 5-5-5 bypass                      | 32K    |

| 2*†  | 0010    | 8B2P1C         | 8 bpp, 2 pixel addresses, 1 PCLK cycle | 8-bit pseudo                             | 256    |

| 3*   | 0011    | 16B1P1C        | 16 bpp, 1 pixel data, 1 PCLK cycle     | 16-bit 5-6-5 bypass                      | 64K    |

| 4*   | 0100    | 8B1P2C (4 + 4) | 8 bpp, 1 pixel address, 2 PCLK cycles  | 8-bit pseudo (4 + 4 pixel data transfer) | 256    |

| 5*   | 0101    | 24B1P2C        | 24 bpp, 1 pixel data, 2 PCLK cycles    | 24-bit 8-8-8 bypass                      | 16.7M  |

| 6*   | 0110    | 16B1P2C        | 16 bpp, 1 pixel data, 2 PCLK cycles    | 16-bit 5-6-5 bypass                      | 64K    |

| 7*   | 0111    | 24B1P3C        | 24 bpp, 1 pixel data, 3 PCLK cycles    | 24-bit 8-8-8 bypass                      | 16.7M  |

| 8*   | 1000    | 8B1P2C (4 + 4) | 8 bpp, 1 pixel address, 2 PCLK cycles  | 8-bit pseudo (4 + 4 pixel data transfer) | 256    |

| 9*   | 1001    | 8B1P2C (8 + 0) | 8 bpp, 1 pixel address, 2 PCLK cycles  | 8-bit pseudo (8 + 0 pixel data transfer) | 256    |

| Α†   | 1010    | 8B2P1C         | 8 bpp, 2 pixel addresses, 1 PCLK cycle | MIX-COLOR®, 8-bit pseudo                 | 256    |

| B†   | 1011    | 24B2P3C        | 24 bpp, 2 pixel data, 3 PCLK cycles    | 24-bit 8-8-8 bypass                      | 16.7M  |

| С    | 1100    | 15B1P2C        | 15 bpp, 1 pixel data, 2 PCLK cycles    | 15-bit 5-5-5 bypass                      | 32K    |

| Dţ   | 1101    | 8B2P1C         | 8 bpp, 2 pixel addresses, 1 PCLK cycle | MIX-COLOR®, 8-bit pseudo                 | 256    |

|      |         |                |                                        |                                          |        |

| Mode | CR[7:4] | MSV            | N = 1, SECONDARY MODE                  | Secondary Mode Description               | Colors |

| 0*   | 0000    | 16B1P1C        | 16 bpp, 1 pixel data, 1 PCLK cycle     | 16-bit 5-6-5 bypass                      | 64K    |

| 1*   | 0001    | 8B1P1C         | 8 bpp, 1 pixel address, 1 PCLK cycle   | 8-bit pseudo                             | 256    |

| 2*†  | 0010    | 8B2P1C         | 8 bpp, 2 pixel addresses, 1 PCLK cycle | 8-bit pseudo                             | 256    |

| 3*   | 0011    | 8B1P1C         | 8 bpp, 1 pixel address, 1 PCLK cycle   | 8-bit pseudo                             | 256    |

| 4*   | 0100    | 24B1P2C        | 24 bpp, 1 pixel data, 2 PCLK cycles    | 24-bit 8-8-8 bypass                      | 16.7M  |

| 5*   | 0101    | 16B1P2C        | 16 bpp, 1 pixel data, 2 PCLK cycles    | 16-bit 5-6-5 bypass                      | 64K    |

| 6*   | 0110    | 24B1P2C        | 24 bpp, 1 pixel data, 2 PCLK cycles    | 24-bit 8-8-8 bypass                      | 16.7M  |

| 7*   | 0111    | 24B1P3C        | 24 bpp, 1 pixel data, 3 PCLK cycles    | 24-bit 8-8-8 bypass                      | 16.7M  |

| 8*   | 1000    | 16B1P2C        | 16 bpp, 1 pixel data, 2 PCLK cycles    | 16-bit 5-6-5 bypass                      | 64K    |

| 9*   | 1001    | 24B1P2C        | 24 bpp, 1 pixel data, 2 PCLK cycles    | 24-bit 8-8-8 bypass                      | 16.7M  |

| At   | 1010    | 15B1P1C        | 15 bpp, 1 pixel data, 1 PCLK cycle     | MIX-COLOR®, 15-bit 5-5-5 bypass          | 32K    |

D† Note:

B†

C

1011

1100

1101

bpp = bits per pixel

24B2P3C

8B1P2C (4 + 4)

16B1P1C

16 bpp, 1 pixel data, 1 PCLK cycle

† = on-chip clock doubler enabled

24 bpp, 2 pixel data, 3 PCLK cycles

8 bpp, 1 pixel address, 2 PCLK cycles

MIX-COLOR®, 16-bit 5-6-5 bypass

\* = ATT20C498 compatible mode

8-bit pseudo (4 + 4 pixel data transfer)

16.7M

256

64K

24-bit 8-8-8 bypass

See Table 2 on page 4-32 for detailed pixel data organization.

#### Mode 0

Primary Mode:

8B1P1C:

8 bpp, 1 pixel address, 1 PCLK cycle, 256 colors

Pixel address for the red, green, and blue color palette is latched on the rising edge of PCLK. Palette RAM contains 256 colors of 256K possible colors (6 bits each for the IOR, IOG, and IOB outputs). Pseudo color pixel address (P[7:0]) is then bit-wise

"AND"ed with the pixel RMR.

Following is the 8B1P1C pixel address transfer format:

| P[15] | P[14] | P[13] | P[12] | P[11] | P[10] | P[9] | P[8] | P[7] | P[6] | P[5] | P[4] | P[3] | P[2] | P[1] | P[0] |

|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|

| X     | Х     | Х     | Х     | Х     | Х     | Χ    | Х    | P7   | P6   | P5   | P4   | P3   | P2   | P1   | P0   |

Note:

bpp = bits per pixel

X = unused bit

P[i] = pixel input pin

P[7:0] = pseudo color pixel address

Secondary Mode:

16B1P1C:

16 bpp (5-6-5), 1 pixel data, 1 PCLK cycle, 64K colors

Pixel data is latched on the rising edge of PCLK. Pixel data is organized as 5 bits of color information for red and blue, and 6 bits of color information for the green color palette. For further information, please refer to **Figure 6** on page 4-45.

Following is the 16B1P1C (5-6-5) pixel data transfer format:

| P[15] | P[14] | P[13] | P[12] | P[11] | P[10] | P[9] | P[8] | P[7] | P[6] | P[5] | P[4] | P[3] | P[2] | P[1] | P[0] |

|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|

| R7    | R6    | R5    | R4    | R3    | G7    | G6   | G5   | G4   | G3   | G2   | B7   | B6   | B5   | B4   | В3   |

Note:

Lowest two or three bits of the DAC inputs are padded with zeros

bpp = bits per pixel

P[i] = pixel input pin

B[7:3] = blue pixel data

R[7:3] = red pixel data

G[7:2] = green pixel data

#### Mode 1

Primary Mode:

15B1P1C:

15 bpp (5-5-5), 1 pixel data, 1 PCLK cycle, 32K colors

Pixel data is latched on the rising edge of PCLK. Pixel data is organized as 5 bits of color information each for the red, green, and blue color palette. For further

information, please refer to Figure 5 on page 4-45.

Following is the 15B1P1C (5-5-5) pixel data transfer format:

| P[15] | P[14] | P[13] | P[12] | P[11] | P[10] | P[9] | P[8] | P[7] | P[6] | P[5] | P[4] | P[3] | P[2] | P[1] | P[0] |

|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|

| X     | R7    | R6    | R5    | R4    | R3    | G7   | G6   | G5   | G4   | G3   | B7   | B6   | B5   | B4   | В3   |

Note: Lowest three bits of the DAC inputs are padded with zeros

bpp = bits per pixel

X = unused bit

P[i] = pixel input pin

R[7:3] = red pixel data

G[7:3] = green pixel data

B[7:3] = blue pixel data

Secondary Mode:

8B1P1C:

8 bpp, 1 pixel address, 1 PCLK cycle, 256 colors

Pixel address for the red, green, and blue color palette is latched on the rising edge of PCLK. Palette RAM contains 256 colors of 256K possible colors (6 bits each for the IOR, IOG, and IOB outputs). Pseudo color pixel address (P[7:0]) is then bit-wise "AND"ed with the pixel RMR.

Following is the 8B1P1C pixel address transfer format:

| P[15] | P[14] | P[13] | P[12] | P[11] | P[10] | P[9] | P[8] | P[7] | P[6] | P[5] | P[4] | P[3] | P[2] | P[1] | P[0] |

|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|

| X     | Х     | Х     | Х     | Х     | Х     | Х    | Х    | P7   | P6   | P5   | P4   | P3   | P2   | P1   | P0   |

Note:

bpp = bits per pixel

X = unused bit

P[i] = pixel input pin

P[7:0] = pseudo color pixel address

### Mode 2

Primary /

Secondary Modes:

8B2P1C:

8 bpp, 2 pixel addresses, 1 PCLK cycle, 256 colors

Pixel addresses for the red, green, and blue color palette are latched on the rising edge of PCLK. Palette RAM contains 256 colors of 256K possible colors (6 bits each for the IOR, IOG, and IOB outputs). Pseudo color pixel addresses (P[7:0]) are then

bit-wise "AND" ed with the RMR.

Following is the 8B2P1C pixel address transfer format:

| P[15] | P[14] | P[13] | P[12] | P[11] | P[10] | P[9] | P[8] | P[7] | P[6] | P[5] | P[4] | P[3] | P[2] | P[1] | P[0] |

|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|

| P7    | P6    | P5    | P4    | Р3    | P2    | P1   | P0   | P7   | P6   | P5   | P4   | P3   | P2   | P1   | P0   |

Note: Internal clock doubler enabled to produce twice the pixel resolution per PCLK period

bpp ≈ bits per pixel

P[i] = pixel input pin

P[7:0] = pseudo color pixel address

#### Mode 3

Primary Mode:

16B1P1C:

16 bpp (5-6-5), 1 pixel data, 1 PCLK cycle, 64K colors

Pixel data is latched on the rising edge of PCLK. Pixel data is organized as 5 bits of color information for red and blue, and 6 bits of color information for the green color palette. For further information, please refer to **Figure 6** on page 4-45.

Following is the 16B1P1C (5-6-5) pixel data transfer format:

| P[15] | P[14] | P[13] | P[12] | P[11] | P[10] | P[9] | P[8] | P[7] | P[6] | P[5] | P[4] | P[3] | P[2] | P[1] | P[0] |

|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|

| R7    | R6    | R5    | R4    | R3    | G7    | G6   | G5   | G4   | G3   | G2   | B7   | B6   | B5   | B4   | В3   |

Note: Lowest two or three bits of the DAC inputs are padded with zeros

bpp = bits per pixel

P[i] = pixel input pin

B[7:3] = blue pixel data

R[7:3] = red pixel data

G[7:2] = green pixel data

Secondary Mode:

QRIDIC.

8 bpp, 1 pixel address, 1 PCLK cycle, 256 colors

Pixel address for the red, green, and blue color palette is latched on the rising edge of PCLK. Palette RAM contains 256 colors of 256K possible colors (6 bits each for the IOR, IOG, and IOB outputs). Pseudo color pixel address (P[7:0]) is then bit-wise "AND"ed with the pixel RMR.

Following is the **8B1P1C** pixel address transfer format:

| P[1 | 5] P[14] | P[13] | P[12] | P[11] | P[10] | P[9] | P[8] | P[7] | P[6] | P[5] | P[4] | P[3] | P[2] | P[1] | P[0] |

|-----|----------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|

| X   | Х        | Х     | Х     | X     | Х     | X    | Х    | P7   | P6   | P5   | P4   | P3   | P2   | P1   | P0   |

Note:

bpp = bits per pixel

X = unused bit

P[i] = pixel input pin

P[7:0] = pseudo color pixel address

#### Mode 4

Primary Mode:

8B1P2C:

8 bpp (4 + 4), 1 pixel address, 2 PCLK cycles, 256 colors

Pixel address for the red, green, and blue color palette is latched on every two consecutive rising edges of PCLK. Palette RAM contains 256 colors of 256K possible colors (6 bits each for the IOR, IOG, and IOB outputs). Pseudo color pixel address (P[7:0]) is then bit-wise "AND"ed with the RMR.

Following is the **8B1P2C** (4 + 4) pixel address transfer:

|     | P[15] | P[14] | P[13] | P[12] | P[11] | P[10] | P[9] | P[8] | P[7] | P[6] | P[5] | P[4] | P[3] | P[2] | P[1] | P[0] |

|-----|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|

| 1st | Х     | Х     | Х     | Х     | Х     | Х     | Х    | Х    | Х    | Х    | Х    | Χ    | P3   | P2   | P1   | P0   |

| 2nd | Х     | Х     | Х     | Х     | Х     | Х     | Х    | Х    | Х    | Х    | Х    | X    | P7   | P6   | P5   | P4   |

Note:

bpp = bits per pixel

X = unused bit

P[i] = pixel input pin

Secondary Mode:

24B1P2C:

24 bpp (8-8-8), 1 pixel data, 2 PCLK cycles, 16.7M colors

Pixel data is latched on every two consecutive rising edges of PCLK. Pixel data is organized as 8 bits of color information each for the red, green, and blue color palette.

Following is the 24B1P2C (8-8-8) pixel data transfer format:

|     | P[15] | P[14] | P[13] | P[12] | P[11] | P[10] | P[9] | P[8] | P[7] | P[6]       | P[5] | P[4] | P[3] | P[2] | P[1] | P[0] |

|-----|-------|-------|-------|-------|-------|-------|------|------|------|------------|------|------|------|------|------|------|

| 1st | G7    | G6    | G5    | G4    | G3    | G2    | G1   | G0   | B7   | <b>B</b> 6 | B5   | B4   | В3   | B2   | B1   | B0   |

| 2nd | Х     | Х     | Х     | Х     | Х     | Х     | Х    | Х    | R7   | R6         | R5   | R4   | R3   | R2   | R1   | R0   |

Note:

bpp = bits per pixel

X = unused bit

P[i] = pixel input pin

R[7:0] = red pixel data

G[7:0] = green pixel data

B[7:0] = blue pixel data

1st = first pixel data latched in

2nd = second pixel data latched in

### Mode 5

Primary Mode:

24B1P2C:

24 bpp (8-8-8), 1 pixel data, 2 PCLK cycles, 16.7M colors

Pixel data is latched on every two consecutive rising edges of PCLK. Pixel data is organized as 8 bits of color information each for the red, green, and blue color palette.

Following is the **24B1P2C** (8-8-8) pixel data transfer format:

|     | P[15] | P[14] | P[13] | P[12] | P[11] | P[10] | P[9] | P[8] | P[7] | P[6] | P[5] | P[4] | P[3] | P[2] | P[1] | P[0] |

|-----|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|

| 1st | G7    | G6    | G5    | G4    | G3    | G2    | G1   | GO   | B7   | B6   | B5   | В4   | В3   | B2   | B1   | B0   |

| 2nd | Х     | Х     | Х     | Х     | Х     | Х     | Х    | X    | R7   | R6   | R5   | R4   | R3   | R2   | R1   | R0   |

Note:

bpp = bits per pixel

X = unused bit

P[i] = pixel input pin

R[7:0] = red pixel data

G[7:0] = green pixel data

B[7:0] = blue pixel data

1st = first pixel data latched in

2nd = second pixel data latched in

Secondary Mode:

16B1P2C:

16 bpp (5-6-5), 1 pixel data, 2 PCLK cycles, 64K colors

Pixel data is latched on every two consecutive rising edges of PCLK. Pixel data is organized as 5 bits of color information for red and blue, and 6 bits of color information for the green color palette. For further information, please refer to **Figure 6** on page 4-45.

Following is the 16B1P2C (5-6-5) pixel data transfer format:

|    | P[ | 15)         | P[14] | P[13] | P[12] | P[11] | P[10] | P[9] | P[8] | P[7] | P[6] | P[5] | P[4] | P[3] | P[2] | P[1] | P[0] |

|----|----|-------------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|

| 1s |    | X           | Х     | Х     | Х     | Х     | Х     | Х    | Х    | G4   | G3   | G2   | B7   | В6   | B5   | B4   | В3   |

| 2n | 1  | <del></del> | Х     | Х     | Х     | Х     | Х     | Х    | Х    | R7   | R6   | R5   | R4   | R3   | G7   | G6   | G5   |

Note:

Lowest two or three bits of the DAC inputs are padded with zeros

bpp = bits per pixel

X = unused bit

P[i] = pixel input pin

R[7:0] = red pixel data

G[7:0] = green pixel data

B[7:0] = blue pixel data

1st = first pixel data latched in

2nd = second pixel data latched in

#### Mode 6

Primary Mode:

16B1P2C:

16 bpp (5-6-5), 1 pixel data, 2 PCLK cycles, 64K colors

Pixel data is latched on every two consecutive rising edges of PCLK. Pixel data is organized as 5 bits of color information for red and blue, and 6 bits of color information for the green color palette. For further information, please refer to

Figure 6 on page 4-45.

Following is the 16B1P2C (5-6-5) pixel data transfer format:

|     | P[15] | P[14] | P[13] | P[12] | P[11] | P[10] | P[9] | P[8] | P[7] | P[6] | P[5] | P[4] | P[3] | P[2] | P[1] | P[0] |

|-----|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|

| 1st | Х     | Х     | Х     | Х     | Х     | X     | Х    | Χ    | G4   | G3   | G2   | B7   | B6   | B5   | B4   | В3   |

| 2nd | Х     | Х     | Х     | Х     | Х     | Х     | Х    | Х    | R7   | R6   | R5   | R4   | R3   | G7   | G6   | G5   |

Note: Lowest two or three bits of the DAC inputs are padded with zeros

bpp = bits per pixel

1st = first pixel data latched in

X = unused bit

P[i] = pixel input pin B[7:3] = blue pixel data

R[7:3] = red pixel data

G[7:2] = green pixel data 2nd = second pixel data latched in

Secondary Mode:

24B1P2C:

24 bpp (8-8-8), 1 pixel data, 2 PCLK cycles, 16.7M colors

Pixel data is latched on every two consecutive rising edges of PCLK. Pixel data is organized as 8 bits of color information each for the red, green, and blue color palette.

Following is the 24B1P2C (8-8-8) pixel data transfer format:

|     | P[15] | P[14] | P[13] | P[12] | P[11] | P[10] | P[9] | P[8] | P[7] | P[6] | P[5] | P[4] | P[3] | P[2] | P[1] | P[0] |

|-----|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|

| 1st | G7    | G6    | G5    | G4    | G3    | G2    | G1   | G0   | B7   | B6   | B5   | B4   | В3   | B2   | B1   | B0   |

| 2nd | X     | Х     | Х     | Х     | Х     | Х     | Х    | Х    | R7   | R6   | R5   | R4   | R3   | R2   | R1   | R0   |

Note:

bpp = bits per pixel

X = unused bit

P[i] = pixel input pin

R[7:0] = red pixel data

G[7:0] = green pixel data

B[7:0] = blue pixel data

1st = first pixel data latched in

2nd = second pixel data latched in

#### Mode 7

Primary /

Secondary Modes:

24B1P3C:

24 bpp (8-8-8), 1 pixel data, 3 PCLK cycles, 16.7M colors

Pixel data is latched on every three consecutive rising edges of PCLK. Pixel data is organized as 8 bits of color information each for the red, green, and blue color palette.

Following is the 24B1P3C (8-8-8) pixel data transfer format:

|     | P[15] | P[14] | P[13] | P[12] | P[11] | P[10] | P[9] | P[8] | P[7] | P[6] | P[5] | P[4] | P[3] | P[2] | P[1] | P[0] |

|-----|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|

| 1st | Х     | Х     | Х     | Х     | Х     | Х     | Х    | Χ    | B7   | B6   | B5   | B4   | В3   | B2   | B1   | B0   |

| 2nd | Х     | Х     | Х     | Х     | Х     | Х     | Х    | Х    | G7   | G6   | G5   | G4   | G3   | G2   | G1   | G0   |

| 3rd | Х     | Х     | Х     | Х     | Х     | X     | X.   | Х    | R7   | R6   | R5   | R4   | R3   | R2   | R1   | R0   |

Note:

bpp = bits per pixel

X = unused bit

P[i] = pixel input pin

R[7:0] = red pixel data

G[7:0] = green pixel data

B[7:0] = blue pixel data

1st = first pixel data latched in

2nd = second pixel data latched in

3rd = third pixel data latched in

### Mode 8

Primary Mode:

8B1P2C:

8 bpp (4 + 4), 1 pixel address, 2 PCLK cycles, 256 colors

Pixel address for the red, green, and blue color palette is latched on every two consecutive rising edges of PCLK. Palette RAM contains 256 colors of 256K possible colors (6 bits each for the IOR, IOG, and IOB outputs). Pseudo color pixel address (P[7:0]) is then bit-wise "AND"ed with the RMR.

Following is the 8B1P2C (4 + 4) pixel address transfer format:

|     | P[15] | P[14] | P[13] | P[12] | P[11] | P[10] | P[9] | P[8] | P[7] | P[6] | P[5] | P[4] | P[3] | P[2] | P[1] | P[0] |

|-----|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|

| 1st | Х     | Х     | Х     | Х     | Х     | Χ     | X    | Х    | Х    | Х    | Х    | Х    | P3   | P2   | P1   | P0   |

| 2nd | X     | Х     | Х     | Х     | Х     | Χ     | Х    | Х    | X    | Х    | Х    | Х    | P7   | P6   | P5   | P4   |

Note:

bpp = bits per pixel

X = unused bit

P[i] = pixel input pin

Secondary Mode:

16B1P2C:

16 bpp (5-6-5), 1 pixel data, 2 PCLK cycles, 64K colors

Pixel data is latched on every two consecutive rising edges of PCLK. Pixel data is organized as 5 bits of color information for red and blue, and 6 bits of color information for the green color palette. For further information, please refer to **Figure** 6 on page 4-45.

Following is the 16B1P2C (5-6-5) pixel data transfer format:

|     | P[15] | P[14] | P[13] | P[12] | P[11] | P[10] | P[9] | P[8] | P[7] | P[6] | P[5] | P[4] | P[3] | P[2] | P[1] | P[0] |

|-----|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|

| 1st | Х     | Х     | Х     | Χ     | Х     | Х     | Х    | Х    | G4   | G3   | G2   | В7   | В6   | B5   | B4   | В3   |

| 2nd | Х     | Х     | Χ     | Х     | Х     | Х     | Х    | Х    | R7   | R6   | R5   | R4   | R3   | G7   | G6   | G5   |

Note:

Lowest two or three bits of the DAC inputs are padded with zeros

bpp = bits per pixel

X = unused bit

P[i] = pixel input pin

R[7:3] = red pixel data

G[7:2] = green pixel data

B[7:3] = blue pixel data

1st = first pixel data latched in

2nd = second pixel data latched in

#### Mode 9

Primary Mode:

8B1P2C:

8 bpp (8 + 0), 1 pixel address, 2 PCLK cycles, 256 colors

Pixel address for the red, green, and blue color palette is latched on every two consecutive rising edges of PCLK. Palette RAM contains 256 colors of 256K possible colors (6 bits each for the IOR, IOG, and IOB outputs). Pseudo color

pixel address (P[7:0]) is then bit-wise "AND" ed with the RMR.

Following is the 8B1P2C (8 + 0) pixel address transfer format:

|     | P[15] | P[14] | P[13] | P[12] | P[11] | P[10] | P[9] | P[8] | P[7] | P[6] | P[5] | P[4] | P[3] | P[2] | P[1] | P[0] |

|-----|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|

| 1st | Х     | X     | Х     | Х     | Х     | Х     | Х    | Х    | P7   | P6   | P5   | P4   | P3   | P2   | P1   | P0   |

| 2nd | Х     | Х     | Χ     | Х     | Х     | Х     | Х    | X    | Х    | Х    | Х    | Х    | Х    | X    | Х    | X    |

Note:

bpp = bits per pixel

X = unused bit

P[i] = pixel input pin

P[7:0] = pseudo color pixel address

1st = first pixel data latched in

2nd = second pixel data latched in

Secondary Mode:

24B1P2C:

24 bpp (8-8-8), 1 pixel data, 2 PCLK cycles, 16.7M colors

Pixel data is latched on every two consecutive rising edges of PCLK. Pixel data is organized as 8 bits of color information each for the red, green, and blue color palette.

Following is the 24B1P2C (8-8-8) pixel data transfer format:

|     | P[15] | P[14] | P[13] | P[12] | P[11] | P[10] | P[9] | P[8] | P[7] | P[6] | P[5] | P[4] | P[3] | P[2] | P[1] | P[0] |

|-----|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|

| 1st | G7    | G6    | G5    | G4    | G3    | G2    | G1   | G0   | B7   | B6   | B5   | B4   | В3   | B2   | B1   | BO   |

| 2nd | Х     | Х     | Х     | Х     | Х     | X     | Х    | Х    | R7   | R6   | R5   | R4   | R3   | R2   | R1   | R0   |

Note:

bpp = bits per pixel

X = unused bit

P[i] = pixel input pin

R[7:0] = red pixel data

G[7:0] = green pixel data

B[7:0] = blue pixel data

1st = first pixel data latched in

2nd = second pixel data latched in

#### Mode A

Primary Mode:

8B2P1C:

8 bpp, 2 pixel addresses, 1 PCLK cycle, 256 colors

Pixel addresses for the red, green, and blue color palette are latched on the rising edge of PCLK. Palette RAM contains 256 colors of 256K possible colors (6 bits each for the IOR, IOG, and IOB outputs). Pseudo color pixel addresses (P[7:0]) are then bit-wise "AND"ed with the RMR.

Following is the **8B2P1C** pixel address transfer format:

| i | P[15] | P[14] | P[13] | P[12] | P[11] | P[10] | P[9] | P[8] | P[7] | P[6] | P[5] | P[4] | P[3] | P[2] | P[1] | P[0] |

|---|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|

|   | P7    | P6    | P5    | P4    | P3    | P2    | P1   | P0   | P7   | P6   | P5   | P4   | P3   | P2   | P1   | P0   |

Note:

Internal clock doubler enabled to produce twice the pixel resolution per PCLK period

bpp = bits per pixel

P[i] = pixel input pin

P[7:0] = pseudo color pixel address

Secondary Mode:

15B1P1C:

15 bpp (5-5-5), 1 pixel data, 1 PCLK cycle, 32K colors

Pixel data is latched on the rising edge of PCLK. Pixel data is organized as 5 bits of color information each for the red, green, and blue color palette. For further information, please refer to **Figure 5** on page 4-45.

Following is the 15B1P1C (5-5-5) pixel data transfer format:

| P[15] | P[14] | P[13] | P[12] | P[11] | P[10] | P[9] | P[8] | P[7] | P[6] | P[5] | P[4] | P[3] | P[2] | P[1] | P[0] |

|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|

| X     | R7    | R6    | R5    | R4    | R3    | G7   | G6   | G5   | G4   | G3   | B7   | В6   | B5   | B4   | В3   |

Note:

Lowest three bits of the DAC inputs are padded with zeros

bpp = bits per pixel

X = unused bit

P[i] = pixel input pin

R[7:3] = red pixel data

G[7:3] = green pixel data

B[7:3] = blue pixel data

#### Mode B

Primary /

Secondary Modes:

24B2P3C:

24 bpp (8-8-8), 2 pixel data, 3 PCLK cycles, 16.7M colors

Pixel data is latched on every three consecutive rising edges of PCLK. Pixel data is organized as 8 bits of color information each for the red, green, and blue color palette.

Following is the **24B2P3C** (8-8-8) pixel data transfer format:

|     | P[15] | P[14] | P[13] | P[12] | P[11] | P[10] | P[9] | P[8] | P[7] | P[6] | P[5] | P[4] | P[3] | P[2] | P[1] | P[0] |

|-----|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|

| 1st | G7    | G6    | G5    | G4    | G3    | G2    | G1   | G0   | В7   | В6   | B5   | B4   | В3   | B2   | В1   | B0   |

| 2nd | B7    | B6    | B5    | B4    | В3    | B2    | В1   | B0   | R7   | R6   | R5   | R4   | R3   | R2   | R1   | R0   |

| 3rd | R7    | R6    | R5    | R4    | R3    | R2    | R1   | R0   | G7   | G6   | G5   | G4   | G3   | G2   | G1   | G0   |

Note:

Internal clock doubler enabled to produce twice the pixel resolution per PCLK period

bpp = bits per pixelR[7:0] = red pixel data P[i] = pixel input pin

G[7:0] = green pixel data

B[7:0] = blue pixel data

1st = first pixel data latched in

2nd = second pixel data latched in

3rd = third pixel data latched in

#### Mode C

Primary Mode:

15B1P2C:

15 bpp (5-5-5), 1 pixel data, 2 PCLK cycles, 32K colors

Pixel data is latched on every two consecutive rising edges of PCLK. Pixel data is organized as 5 bits of color information each for the red, green, and blue color

palette. For further information, please refer to Figure 5 on page 4-45.

Following is the 15B1P2C (5-5-5) pixel data transfer format:

|     | P[15] | P[14] | P[13] | P[12] | P[11] | P[10] | P[9] | P[8] | P[7] | P[6] | P[5] | P[4]       | P[3] | P[2]       | P[1] | P[0] |

|-----|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------------|------|------------|------|------|

| 1st | Х     | Х     | Х     | Х     | Х     | Х     | Х    | Х    | G5   | G4   | G3   | <b>B</b> 7 | B6   | <b>B</b> 5 | B4   | В3   |

| 2nd | Х     | Х     | Х     | Х     | Х     | Χ     | Х    | Х    | Х    | R7   | R6   | R5         | R4   | R3         | G7   | G6   |

Note:

Lowest three bits of DAC inputs are padded with zeros

bpp = bits per pixel

X = unused bit

P[i] = pixel input pin

R[7:3] = red pixel data

G[7:3] = green pixel data

B[7:3] = blue pixel data

1st = first pixel data latched in

2nd = second pixel data latched in

Secondary Mode:

8B1P2C:

8 bpp (4 + 4), 1 pixel address, 2 PCLK cycles, 256 colors

Pixel address for the red, green, and blue color palette is latched on every two consecutive rising edges of PCLK. Palette RAM contains 256 colors of 256K possible colors (6 bits each for the IOR, IOG, and IOB outputs). Pseudo color pixel address (P[7:0]) is then bit-wise "AND"ed with the RMR.

Following is the 8B1P2C (4 + 4) pixel address transfer format:

|     | P[15] | P[14] | P[13] | P[12] | P[11] | P[10] | P[9] | P[8] | P[7] | P[6] | P[5] | P[4] | P[3] | P[2] | P[1] | P[0] |

|-----|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|

| 1st | Х     | Х     | Х     | Х     | Х     | Х     | Х    | Х    | Х    | Х    | Х    | Х    | P3   | P2   | P1   | P0   |

| 2nd | Х     | Х     | Х     | Х     | Х     | Х     | Χ    | Х    | Χ    | Х    | Х    | Х    | P7   | P6   | P5   | P4   |

Note:

bpp = bits per pixel

X = unused bit

P[i] = pixel input pin

### Mode D

Primary Mode:

8B2P1C:

8 bpp, 2 pixel addresses, 1 PCLK cycle, 256 colors

Pixel addresses for the red, green, and blue color palette are latched on the rising edge of PCLK. Palette RAM contains 256 colors of 256K possible colors (6 bits each for the IOR, IOG, and IOB outputs). Pseudo color pixel addresses (P[7:0]) are then

bit-wise "AND" ed with the RMR.

Following is the 8B2P1C pixel address transfer format:

| P[15] | P[14] | P[13] | P[12] | P[11] | P[10] | P[9] | P[8] | P[7] | P[6] | P[5] | P[4] | P[3] | P[2] | P[1] | P[0] |

|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|

| P7    | P6    | P5    | P4    | P3    | P2    | P1   | P0   | P7   | P6   | P5   | P4   | P3   | P2   | P1   | P0   |

Note:

Internal clock doubler enabled to produce twice the pixel resolution per PCLK period

bpp = bits per pixel

P[7:0] = pseudo color pixel address

P[i] = pixel input pin

Secondary Mode:

16B1P1C:

16 bpp (5-6-5), 1 pixel data, 1 PCLK cycle, 64K colors

Pixel data is latched on the rising edge of PCLK. Pixel data is organized as 5 bits of color information for red and blue, and 6 bits of color information for the green color palette. For further information, please refer to **Figure 6** on page 4-45.

Following is the 16B1P1C (5-6-5) pixel data transfer format:

| P[15] | P[14] | P[13] | P[12] | P[11] | P[10] | P[9] | P[8] | P[7] | P[6] | P[5] | P[4] | P[3] | P[2] | P[1] | P[0] |

|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|

| R7    | R6    | R5    | R4    | R3    | G7    | G6   | G5   | G4   | G3   | G2   | B7   | В6   | B5   | B4   | В3   |

Note:

Lowest two or three bits of DAC inputs are padded with zeros

bpp = bits per pixel

P[i] = pixel input pin

R[7:3] = red pixel data

G[7:2] = green pixel data

B[7:3] = blue pixel data

# Hardware and Software Mode Switching

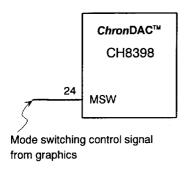

Hardware mode switching:

The external mode control pin (MSW) is used to switch between primary and secondary modes and requires bit 2 (MSDIS) = 0 (default value) in the

Control Register (CR).

Primary mode:

MSW = 0

Secondary mode:

MSW = 1

### Hardware mode switching

The external MSW signal (pin 24) handles the hardware mode switching for CH8398.

The mode switching control signal from the graphics controller drives the MSW input on CH8398.

Figure 3: Hardware Mode Switching

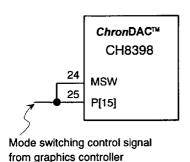

Software (embedded) mode switching:

The mode control signal is used to switch between primary and

secondary modes and is embedded in the pixel data.

Embedded switching can be applied to modes 1, 8, A, and C.

Mode A

Primary mode:

P[7] and P[15] = 0

Secondary mode:

P[15] = 1

Modes 1, 8, and C

Primary mode:

P[15] = 0

Secondary mode:

P[15] = 1

## Software mode switching

CH8398 handles software or embedded mode switching by connecting MSW and P[15] pins.

The mode switching control signal from the graphics controller drives MSW and P[15] inputs on CH8398.

Note: Design flexibility utilizing either hardware or software (embedded) mode switching may be achieved by connecting pins through a 0  $\Omega$  resistor

Figure 4: Software Mode Switching

Note:

Hardware mode switching method applies to all display modes Software mode switching method is limited to certain display modes

# **Bypass Mode Diagrams**

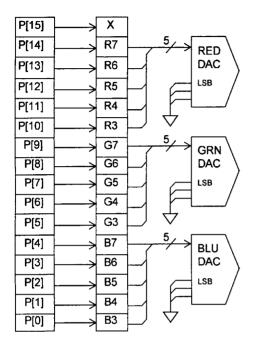

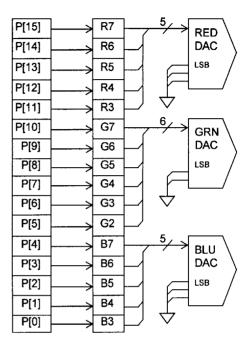

Figure 5: 15-bit bypass mode (used in Modes 1, A, C)

Figure 6: 16-bit bypass mode (used in Modes 0, 3, 5, 6, 8, D)

Note: Lowest two or three bits of DAC inputs are padded with zeros

P[i] = pixel input pin

R[7:3] = red pixel data

G[7:2] = green pixel data

B[7:3] = blue pixel data

Table 3 • Pixel Data Organization

| P[15:8]   X                                                                                                                            | Organization of Pixel Inputs          | MSW = 1 | Organization                                              | Organization of Pixel Inputs |

|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------|-----------------------------------------------------------|------------------------------|

| 8B1P1C       X X X X X X X X X X X X X X X X X X X                                                                                     | 15:8] P[7:0]                          | Second  | P[15:8]                                                   | P[7:0]                       |

| 15B1P1C XR7 R6 R5 R4 R3 G7 G6 8B2P1C P7 P6 P5 P4 P3 P2 P1 P0 16B1P1C X X X X X X X X X X X X X X X X X X X                             | ×                                     | 16B1P1C | R7 R6 R5 R4 R3 G7 G6 G5                                   | G4 G3 G2 B7 B6 B5 B4 B3      |

| 8B2P1C P7 P6 P5 P4 P3 P2 P1 P0 16B1P1C X X X X X X X X X X X X X X X X X X X                                                           | R4 R3 G7 G6 G5 G4 G3 B7 B6 B5 B4 B3   | 8B1P1C  | × × × × × × ×                                             | P7 P6 P5 P4 P3 P2 P1 P0      |

| 16B1P1C R7 R6 R5 R4 R3 G7 G6 G5 8B1P2C X X X X X X X X X X X X X X X X X X X                                                           | P3 P2 P1 P0 P7 P6 P5 P4 P3 P2 P1 P0   | 8B2P1C  | P7 P6 P5 P4 P3 P2 P1 P0                                   | P7 P6 P5 P4 P3 P2 P1 P0      |

| 8B1P2C       X X X X X X X X X X X X X X X X X X X                                                                                     | 99                                    | 8B1P1C  | × × × × × × ×                                             | P7 P6 P5 P4 P3 P2 P1 P0      |

| (4+4)       X X X X X X X X X X X X X X X X X X X                                                                                      | ×                                     | 24B1P2C | G7 G6 G5 G4 G3 G2 G1 G0                                   | B7 B6 B5 B4 B3 B2 B1 B0      |

| 24B1P2C G7 G6 G5 G4 G3 G2 G1 G0  X X X X X X X X X X X X X X X X X X X                                                                 | ×××                                   |         | × × × × × × ×                                             | R7 R6 R5 R4 R3 R2 R1 R0      |

| 16B1P2C       X X X X X X X X X X X X X X X X X X X                                                                                    | 4 G3 G2 G1 G0 B7 B6 B5 B4 B3 B2 B1 B0 | 16B1P2C | × × × × × × ×                                             | G4 G3 G2 B7 B6 B5 B4 B3      |

| 16B1P2C                                                                                                                                | ×                                     |         | × × × × × × ×                                             | R7 R6 R5 R4 R3 G7 G6 G5      |

| 24B1P3C       X X X X X X X X X X X X X X X X X X X                                                                                    | ×                                     | 24B1P2C | G7 G6 G5 G4 G3 G2 G1 G0                                   | B7 B6 B5 B4 B3 B2 B1 B0      |

| 24B1P3C                                                                                                                                | ×                                     |         | × × × × × × ×                                             | R7 R6 R5 R4 R3 R2 R1 R0      |

| 8B1P2C                                                                                                                                 | ×                                     | 24B1P3C | x x x x x x x x                                           | B7 B6 B5 B4 B3 B2 B1 B0      |

| 8B1P2C                                                                                                                                 | ×                                     |         | × × × × × × ×                                             | G7 G6 G5 G4 G3 G2 G1 G0      |

| 8B1P2C X X X X X X X X X X X X X X X X X X X                                                                                           | ×                                     |         | $\times$ $\times$ $\times$ $\times$ $\times$ $\times$     | R7 R6 R5 R4 R3 R2 R1 R0      |

| (4+4) X X X X X X X X X X X X X X X X X X X                                                                                            | ×                                     | 16B1P2C | x x x x x x x x                                           | G4 G3 G2 B7 B6 B5 B4 B3      |

| 8B1P2C X X X X X X X X X X X X X X X X X X X                                                                                           | ×                                     |         | × × × × × × ×                                             | R7 R6 R5 R4 R3 G7 G6 G5      |

| (8+0) X X X X X X X X X X X X X X X X X X X                                                                                            | ×                                     | 24B1P2C | G7 G6 G5 G4 G3 G2 G1 G0                                   | B7 B6 B5 B4 B3 B2 B1 B0      |

| 8B2P1C P7 P6 P5 P4 P3 P2 P1 P0 24B2P3C G7 G6 G5 G4 G3 G2 G1 G0 B7 B6 B5 B4 B3 B2 B1 B0 R7 R6 R5 R4 R3 R2 R1 R0 15B1P2C X X X X X X X X | ×                                     |         | × × × × × × ×                                             | R7 R6 R5 R4 R3 R2 R1 R0      |

| 24B2P3C G7 G6 G5 G4 G3 G2 G1 G0<br>B7 B6 B5 B4 B3 B2 B1 B0<br>R7 R6 R5 R4 R3 R2 R1 R0<br>15B1P2C X X X X X X X                         | P3 P2 P1 P0 P7 P6 P5 P4 P3 P2 P1 P0   | 15B1P1C | X R7 R6 R5 R4 R3 G7 G6                                    | G5 G4 G3 B7 B6 B5 B4 B3      |

| B7 B6 B5 B4 B3 B2 B1 B0 R7 R6 R5 R4 R3 R2 R1 R0 15B1P2C X X X X X X X                                                                  | 4 G3 G2 G1 G0 B7 B6 B5 B4 B3 B2 B1 B0 | 24B2P3C | G7 G6 G5 G4 G3 G2 G1 G0                                   | B7 B6 B5 B4 B3 B2 B1 B0      |

| R7 R6 R5 R4 R3 R2 R1 R0   15B1P2C   X                                                                                                  | B3 B2 B1 B0 R7 R6 R5 R4 R3 R2 R1 R0   |         | B7 B6 B5 B4 B3 B2 B1 B0                                   | R7 R6 R5 R4 R3 R2 R1 R0      |

| 15B1P2C X X X X X X X X X X X X X X X X X X X                                                                                          | 1 R3 R2 R1 R0 G7 G6 G5 G4 G3 G2 G1 G0 |         | R7 R6 R5 R4 R3 R2 R1 R0                                   | G7 G6 G5 G4 G3 G2 G1 G0      |

|                                                                                                                                        | ×                                     | 8B1P2C  | $\times \times \times \times \times \times \times \times$ | X X X P3 P2 P1 P0            |

| ×<br>×<br>×                                                                                                                            | X X X X X X R7 R6 R5 R4 R3 G7 G6      | (4 + 4) | $\times$ $\times$ $\times$ $\times$ $\times$ $\times$     | X X X P7 P6 P5 P4            |

| Dt 8B2P1C P7 P6 P5 P4 P3 P2 P1 P0 P7                                                                                                   | P3 P2                                 | 16B1P1C | R7 R6 R5 R4 R3 G7 G6 G5                                   | G4 G3 G2 B7 B6 B5 B4 B3      |

\* = ATT20C498 compatible mode Note: † = on-chip clock doubler enabled

$\label{eq:pixel} Pi = pixel \ input \ for \ pseudo-color \ mode, \ where \ i \ indicates \ pixel \ bit \ number \ X = unused \ bits$ Bi, Gi, Ri = pixel input for bypass mode, where i indicates pixel bit number

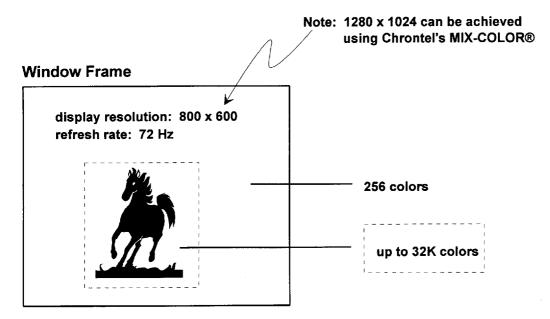

## **MIX-COLOR®**

CH8398 offers an enhanced feature called MIX-COLOR® mode, which allows the simultaneous display of image regions with different spatial resolution and color depth in a single bitmapped frame. MIX-COLOR® is capable of displaying 64K colors within a high resolution (1280 x 1024 @ 75 Hz) graphics window. This feature is particularly useful in Windows® applications where a colorful picture is placed within a page of text.

## Window Frame High spatial resolution Introduction MIX-COLOR® is Chrontel's unit Display Resolution: 1280 x 1024 two sivin modes each having a disk depth. These two modes (Primary: Refresh Rate: 75 Hz simultaneously or one at a time with switching pat the Primary and Seco Chrontel MIX-COLOR® is available 128 colors or 256 colors and CH8391 8-bit pixel nicolle Chre CH8388 ChronDAC™ MIX-COLO MIX-COLOR® made in CH8398 is ! ing can be implemented with craig-High color depth Display Resolution: 640 x 1024 (equivalent full-screen resolution) 32K colors or 64K colors

Figure 7: MIX-COLOR® Mode

MIX-COLOR® mode is available in modes A and D:

| M | od | 6 | Δ |

|---|----|---|---|

|   |    |   |   |

Primary mode: Pseudo-color mode

embedded mode: 128 colors hardware mode: 256 colors

Secondary mode: Bypass color mode

embedded mode: 32K colors

hardware mode: 32K colors

Mode D

Primary mode: Pseudo-color mode

hardware mode: 256 colors

Secondary mode: Bypass color mode

hardware mode: 64K colors

# Comparison of MIX-COLOR® and PixMix™ Modes

CH8398 supports both MIX-COLOR® and PixMix<sup>TM</sup> modes for displaying high resolution graphics in addition to high color depth within the same frame of data.

#### MIX-COLOR®

- MIX-COLOR® has flexibility for both on-the-fly hardware and software (embedded) switching modes.

- MIX-COLOR® maintains the maximum possible resolution for the given clock rate by utilizing all pixel data available.

- · 2 pixel addresses per pixel clock.

- MIX-COLOR® efficiently correlates pixel data stored in memory with pixel data displayed.

- MIX-COLOR® simultaneously displays bypass and pseudo-color modes with the following specs:

Bypass mode: 16-bit or 64K colors Pseudo-color mode: 256 colors Standard resolution (max): 1280 x 1024 @ 75 Hz

#### PixMix<sup>TM</sup>

- PixMix<sup>TM</sup> implementation is only available in the embedded switching mode.

- PixMix™ pixel resolution does not fully utilize the pixel bus bandwidth or the frame buffer memory pixel data.

- · 1 pixel address per pixel clock.

- PixMix<sup>TM</sup> inefficiently maps between pixel data stored in memory with pixel data displayed.

- PixMix<sup>TM</sup> simultaneously displays bypass and pseudo-color modes with the following specs:

Bypass mode: 15-bit or 32K colors Pseudo-color mode: 256 colors Standard resolution (max): 800 x 600 @ 72 Hz

Figure 8: PixMix™ Mode

# Examples of Embedded Mode Switching for MIX-COLOR® and PixMix™

Example # 1: Embedded mode switching for MIX-COLOR®

Mode A

Primary mode:

Pseudo-color mode

P[7] and P[15] set to 0

Secondary mode:

Bypass color mode

P[15] set to 1

|        | P[15] | P[14] | P[13] | P[12] | P[11] | P[10] | P[9] | P[8] | P[7] | P[6] | P[5] | P[4] | P[3] | P[2] | P[1] | P[0] |

|--------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|

| Pseudo | 0     | P6    | P5    | P4    | P3    | P2    | P1   | P0   | 0    | P6   | P5   | P4   | P3   | P2   | P1   | P0   |

| 5-5-5  | 1     | R7    | R6    | R5    | R4    | R3    | G7   | G6   | G5   | G4   | G3   | В7   | В6   | B5   | B4   | ВЗ   |

Note:

Embedded case requires palette RAM table to be reconfigured for 128 colors instead of 256 colors

P[i] = pixel input pin

R[7:3] = red pixel data

G[7:3] = green pixel data

B[7:3] = blue pixel data

CH8398 is capable of implementing PixMix™ mode, using P[15] as a mode switch control signal.

Example #2: Embedded mode switching for PixMix<sup>TM</sup>

Mode\_1

Primary mode:

Bypass color mode

P[15] set to 0

Secondary mode:

Pseudo-color mode

P[15] set to 1

|        | P[15] | P[14] | P[13] | P[12] | P[11] | P[10] | P[9] | P[8] | P[7] | P[6] | P[5] | P[4] | P[3] | P[2]       | P[1] | P[0] |

|--------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------------|------|------|

| 5-5-5  | 0     | R7    | R6    | R5    | R4    | R3    | G7   | G6   | G5   | G4   | G3   | B7   | B6   | <b>B</b> 5 | B4   | В3   |

| Pseudo | 1     | X     | X     | Х     | Х     | Х     | Х    | Х    | P7   | P6   | P5   | P4   | P3   | P2         | P1   | P0   |

Note:

P[i] = pixel input pin

P[7:0] = pseudo pixel address

X = unused bit

R[7:3] = red pixel data

G[7:3] = green pixel data

B[7:3] = blue pixel data

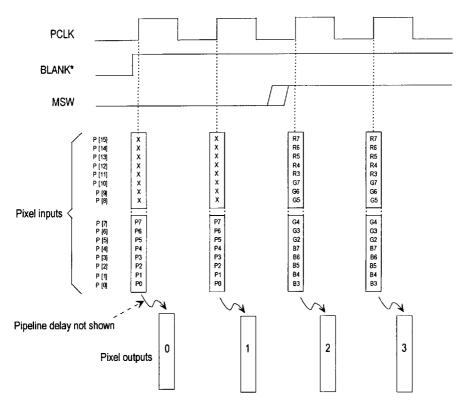

# **PCLK Timing Diagrams**

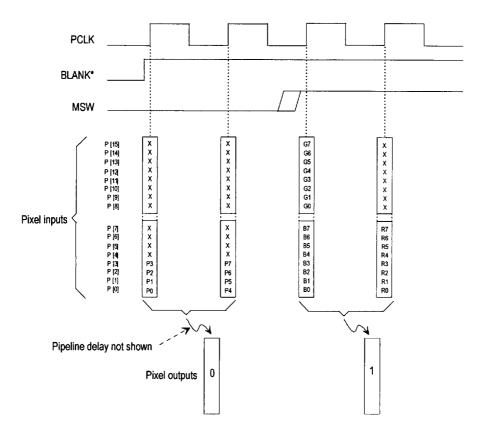

Primary mode: 8-bit pseudo (8B1P1C) Secondary mode: 16-bit bypass (16B1P1C)

Figure 9: PCLK Timing Mode 0 Using Hardware Mode Switching<sup>1</sup>

| 1 | Mode | CR[7] | CR[6] | CR[5] | CR[4] | Primary Mode | Secondary Mode      |

|---|------|-------|-------|-------|-------|--------------|---------------------|

| 1 | 0    | 0     | 0     | 0     | 0     | 8-bit pseudo | 16-bit 5-6-5 bypass |

Note: CR[7:4] corresponds to display mode control bits located in the control register

1 Figures 9 through 12 represent the most commonly used options For information on other available options, please call Chrontel

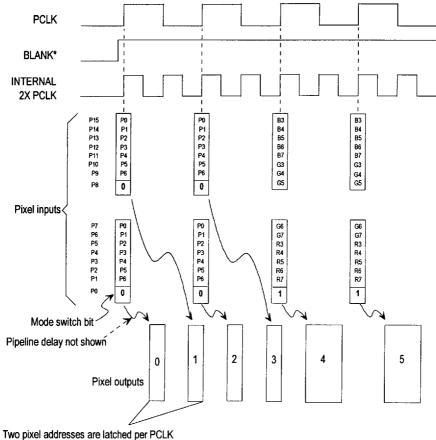

# **PCLK Timing Diagrams (continued)**

Primary mode: 8-bit pseudo (8P1P2C)

Secondary mode: 24-bit bypass (24B1P2C)

Figure 10: PCLK Timing for Mode 4 Using Hardware Mode Switching<sup>1</sup>

| Ī | Mode | CR[7] | CR[6] | CR[5] | CR[4] | Primary Mode       | Secondary Mode      |

|---|------|-------|-------|-------|-------|--------------------|---------------------|

| I | 4    | 1     | 0     | 0     | 0     | 8-bit pseudo (4+4) | 24-bit 8-8-8 bypass |

Note: CR[7:4] corresponds to display mode control bits located in the control register

<sup>1</sup> Figures 9 through 12 represent the most commonly used options For information on other available options, please call Chrontel

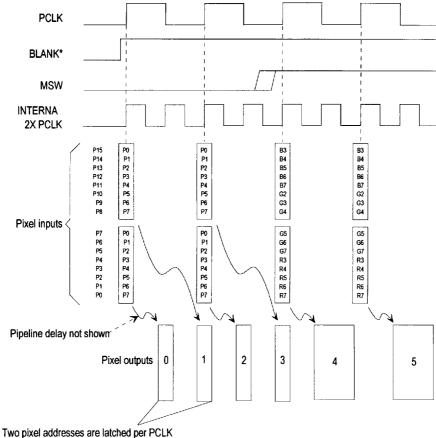

# **PCLK Timing Diagrams (continued)**

**Primary Mode:** 8-bit pseudo (8B2P1C) Secondary Mode: 15-bit bypass (15B1P1C)

Figure 11: PCLK Timing for Mode A, MIX-COLOR®, Using Software Mode Switching<sup>1</sup>

| Mode | CR[7] | CR[6] | CR[5] | CR[4] | Primary Mode            | Secondary Mode                 |

|------|-------|-------|-------|-------|-------------------------|--------------------------------|

| Α    | 1     | 0     | 1     | 0     | MIX-COLOR® 8-bit pseudo | MIX-COLOR® 15-bit 5-5-5 bypass |

Note: CR[7:4] corresponds to display mode control bits located in the control register

Figures 9 through 12 represent the most commonly used options For information on other available options, please call Chrontel

# **PCLK Timing Diagrams (continued)**

Primary Mode: 8-bit pseudo (8B2P1C) Secondary Mode: 16-bit bypass (16B1P1C)

Figure 12: PCLK Timing for Mode D, MIX-COLOR®, Using Hardware Mode Switching<sup>1</sup>

| Mode | CR[7] | CR[6] | CR[5] | CR[4] | Primary Mode            | Secondary Mode                 |

|------|-------|-------|-------|-------|-------------------------|--------------------------------|

| D    | 1     | 1     | 0     | 1     | MIX-COLOR® 8-bit pseudo | MIX-COLOR® 16-bit 5-6-5 bypass |

Note: CR[7:4] corresponds to display mode control bits located in the control register

Figures 9 through 12 represent the most commonly used options For information on other available options, please call Chrontel

Table 4 • Register Maps and Definitions

|                   | RS3 | RS2 | RS1      | RS0 | Description                                                                  | Default upon<br>Power Up |

|-------------------|-----|-----|----------|-----|------------------------------------------------------------------------------|--------------------------|

| PWA               | 1   | 0   | 0        | 0   | Palette RAM Write Address Register                                           | N/A                      |

| PDR               | 1   | 0   | 0        | 1   | Palette RAM Data Register                                                    | N/A                      |

| RMR               | 1   | 0   | 1        | 0   | Pixel Read Mask Register (IDR, alternate access to control register)         | IDR = C0H<br>CR = 00H    |

| PRA               | 1   | 0   | 1        | 1   | Palette RAM Read Address Register                                            | N/A                      |

| CWA               | 0   | 1   | 0        | 0   | Clock RAM Write Address Register (alternate access to clock select register) | N/A                      |

| CDR               | 0   | 1   | 0        | 1   | Clock RAM Data Register                                                      | N/A                      |

| CR <sup>1</sup>   | 0   | 1   | 1        | 0   | Control Register                                                             | 00H                      |

| CRA               | 0   | 1   | 1        | 1   | Clock RAM Read Address Register                                              | N/A                      |

| CSR <sup>1</sup>  | 1   | 0   | 0        | 0   | Clock Select Register                                                        | 00H                      |

| IDR               | 1 - |     | T —      | -   | Identification Register                                                      | COH                      |

| TEST <sup>1</sup> | 0   | 0   | 0        | 1   | Test Register (internal use only)                                            | _                        |

| AUX <sup>2</sup>  | 1 — | _   | <b>—</b> | l – | Auxiliary Register                                                           | 00H                      |

Note:

- 1 These registers can also be accessed by using the alternate accessing method

- 2 This register can only be accessed by using the alternate accessing method

## PWA: Palette RAM Write Address Register

PWA specifies the address to the palette RAM for write access.

## PDR: Palette RAM Data Register

PDR contains the data read from the palette RAM or the data to be written to the RAM. The read address is specified by PRA, the write address is specified by PWA.

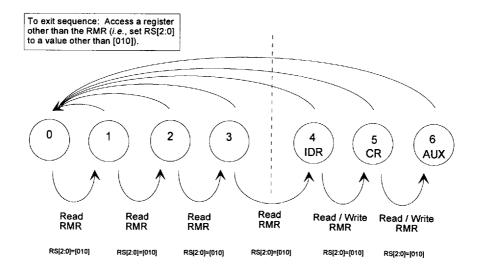

### RMR: Read Mask Register

RMR is used in pseudo and MIX-COLOR® modes. Each bit of RMR is bit-wise logically "AND"ed with the 8-bit palette RAM address. The resulting address is used to point to the palette RAM. Under the alternate register access method, this register is used to access the ID Register, Control Register, Auxiliary Register, and Test Register. For further information, please refer to "Alternate Access Method" on page 4-61.

**Note:** This register is **NOT** initialized upon power up

When pseudo mode is activated, the pixel address uses the RMR. The RMR content is bitwise "AND"ed with the pixel address, and the result is used to address the color palette RAM. On the 15-bit or 16-bit bypass mode, the lowest 2 or 3 bits of the DACs are padded with zeros For further information, please refer to **Figures 5** and **6** on page 4-45. In MIX-COLOR® mode, the masking operation is enabled for pseudo-color mode. To disable the masking operation, write FFH into the RMR.

## PRA: Palette RAM Read Address Register

PRA specifies the address to the palette RAM for read access.

## CWA: PLL Clock RAM Write Address Register

CWA specifies the address to the PLL RAM for write access. Using the alternate register access, CWA accesses the Clock Select Register. For further information, please refer to "Alternate Access Method" on page 4-61.

## CDR: PLL Clock RAM Data Register

CDR contains data read from the PLL RAM or data to be written to the RAM. CRA specifies the read address and CWA specifies the write address.

## CR: Control Register

CR determines the display modes, power down modes, and MPU interface to the color palette RAM.

| CR[7] | CR[6] | CR[5] | CR[4] | CR[3] | CR[2] | CR[1] | CR[0] |

|-------|-------|-------|-------|-------|-------|-------|-------|

| DM3   | DM2   | DM1   | DM0   | PD1   | MSDIS | V/P   | PD0   |

## CR[0]:PD0 = Power Down control bit 0

These power down modes are well-suited for both LCD and CRT applications, and support "Green PC" applications. CH8398 supports both LCD graphics-only controllers and LCD graphics controllers with simultaneous CRT and LCD display. Power consumption of the graphics subsystem can be greatly reduced using these power down modes.

## CR[1]:V / P = Select VCLK / PCLK ratio

If:

the MNK values of VCLK are chosen so VCLK / PCLK = 1,

then:

$$set CR[1] = 0$$

This is used only for optimization of the internal doubler.

Please note that whether CR[1] is set to "0" or "1," a change may not be readily apparent to the user.

For example: PCLK = 28.322 MHz, and the VGA controller requires VCLK = 2 x PCLK

Step 1. Program the proper M, N, and K values in the PLL RAM to generate 56.444 MHz (i.e., M = 21, N = 174, K = 1)

Step 2. Set CR[1] = 1

This example requires the following data format:

|    | MSB |    |    |    |    |    |    |    |    |    | LS | SB |    |    |    |

|----|-----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| D7 | D6  | D5 | D4 | D3 | D2 | D1 | DO | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| 0  | 1   | 0  | 1  | 0  | 1  | 0  | 1  | 1  | 0  | 1  | 0  | 1  | 1  | 1  | 0  |

### CR[2]: MSDIS = MSW input pin disable

0 = MSW pin control display mode switching (default)

1 = MSW pin in interpreted as 0 regardless of its state

CR[3]: PD1 = Power Down control bit 1

CR:

**Control Register (continued)**

Table 5 • Power Down Control Bits.

| CR[3] | CR[0] |                                                                                                                                                                                        |

|-------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|